# TROUBLESHOOTING & REPAIRING YOUR COMMODORE 64

ART MARGOLIS

# TROUBLESHOOTING & REPAIRING YOUR

# TROUBLESHOOTING & REPAIRING YOUR COMMODORE 64

ART MARGOLIS

#### FIRST EDITION

#### FOURTH PRINTING

Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Copyright © 1985 by TAB BOOKS Inc.

Library of Congress Cataloging in Publication Data

Margolis, Art. Troubleshooting and repairing your Commodore 64.

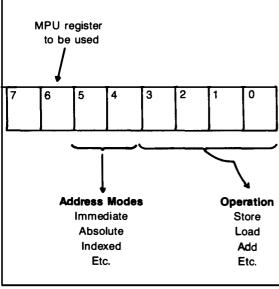

On t.p. the registered trademark symbol "TM" is superscript following "64" in the title. Includes index. 1. Microcomputers—Maintenance and repair. 2. Commodore 64 (Computer) I. Title. TK7887.M374 1985 621.3819'584 85-4640 ISBN 0-8306-0889-3 ISBN 0-8306-1889-9 (pbk.)

Questions regarding the content of this book should be addressed to:

Reader Inquiry Branch Editorial Department TAB BOOKS Inc. P.O. Box 40 Blue Ridge Summit, PA 17214

# Contents

| Te           | Test Point Charts                                                                                                                                                                                                                                                                                                                                                             |    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction |                                                                                                                                                                                                                                                                                                                                                                               |    |

| 1            | Interpreting the Symptoms<br>Common Symptoms 1<br>Dead Computer—Garbage Display—Empty Display Block—No Color—No Video, Sound OK—No<br>Sound—External Device Troubles<br>Diagnostic Programming 5<br>PEEK and POKE—Diagnostic Programs<br>Inside the 64 8<br>Complex Interface Adapter—Microprocessor—Video Interface Chip—Sound Interface Device<br>Troubleshooting Charts 15 | 1  |

| 2            | Disassembly<br>Removing the Top 16<br>Removing the Circuit Board 19<br>Disassembly as a Cure 24<br>Visual Inspection 26<br>Ground Plane Short—Board Defects<br>Cleaning 28<br>Static Electricity 28<br>What Is It?—Wrist Strap—Additional Problems                                                                                                                            | 16 |

| 3            | Chip Location Guide                                                                                                                                                                                                                                                                                                                                                           | 31 |

Drawing a Guide 31 Chip Survey 34

|   | Microprocessor—Complex Interface Adapters—Video Interface Chip—Sound Interface Device—<br>Random Access Memory—BASIC ROM—Kernal ROM—Character ROM—Color RAM—Other Board<br>Landmarks<br>Sockets 39                                                                                                                                                              |     |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | Using the Location Guide 40                                                                                                                                                                                                                                                                                                                                     |     |

| 4 | Chip Changing Techniques                                                                                                                                                                                                                                                                                                                                        | 42  |

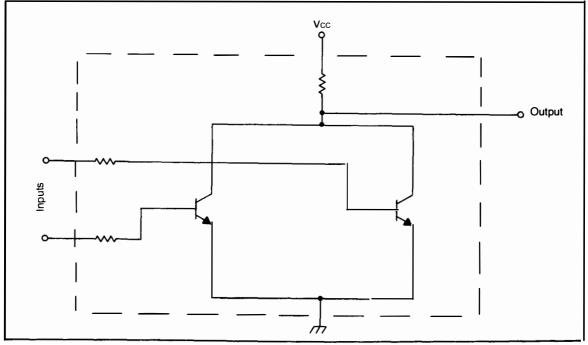

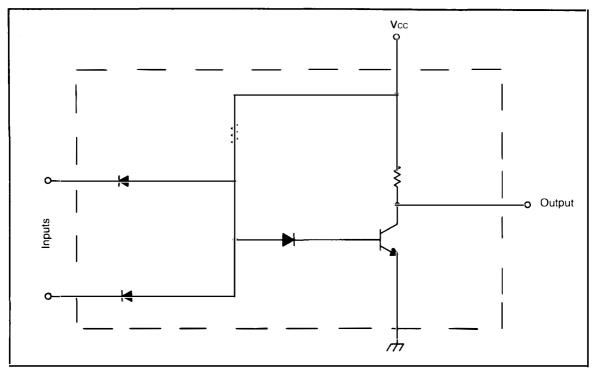

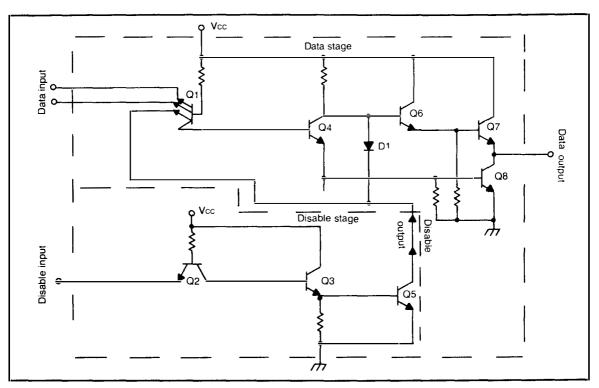

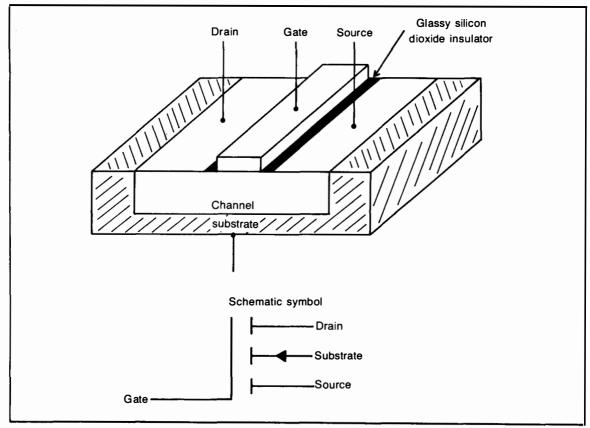

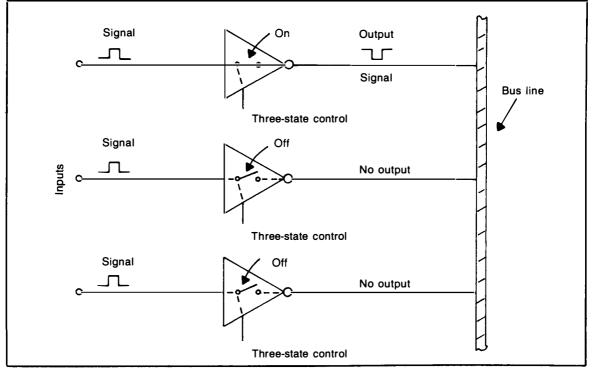

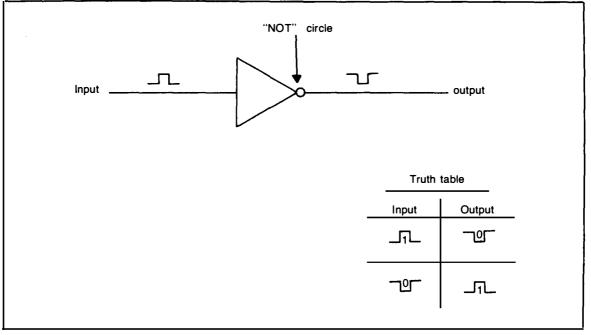

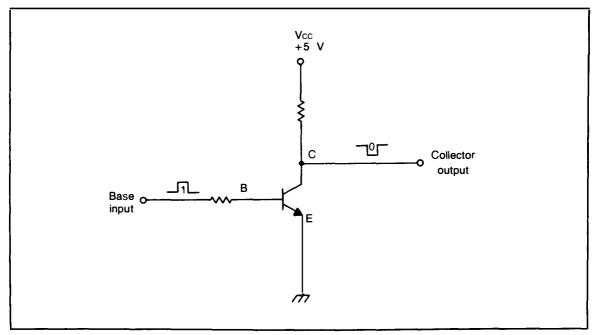

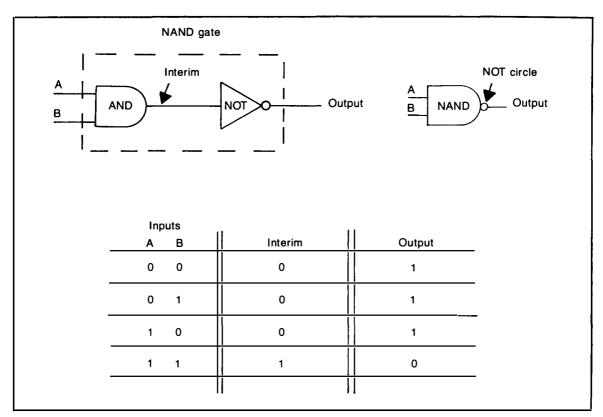

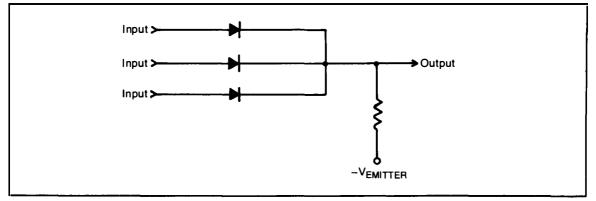

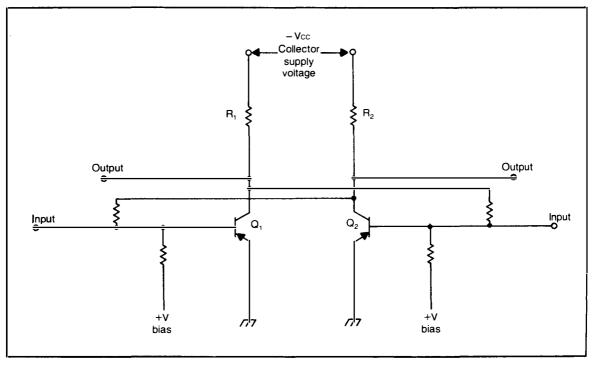

|   | TTL, DTL, and RTL 42<br>Three-State TTL 46<br>MOS Chips 48<br>DIP Package 50<br>Socketed Chips 52<br>Chip Removal—Chip Replacement<br>Soldered-In Chips 55<br>Desoldering—Resoldering                                                                                                                                                                           |     |

| 5 | LSI Chips                                                                                                                                                                                                                                                                                                                                                       | 57  |

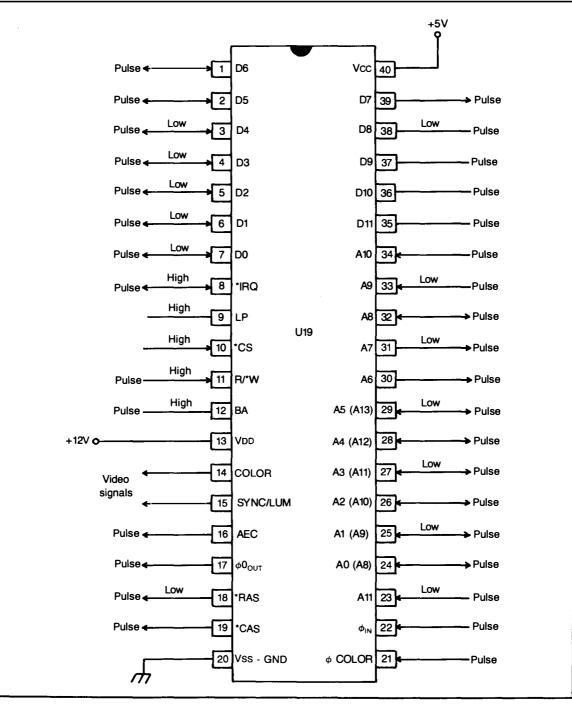

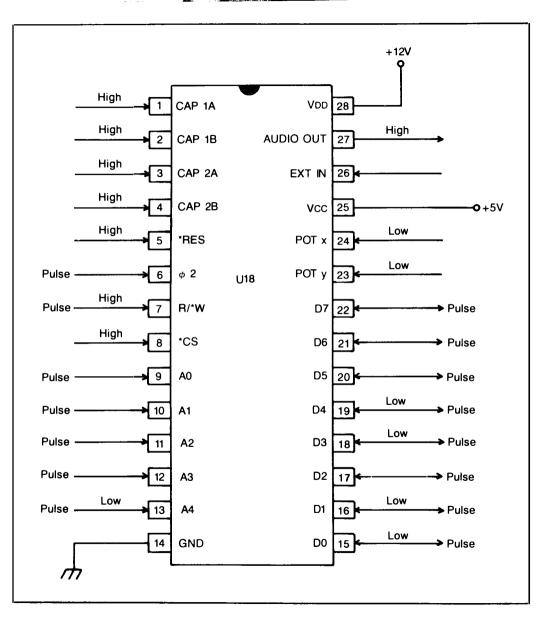

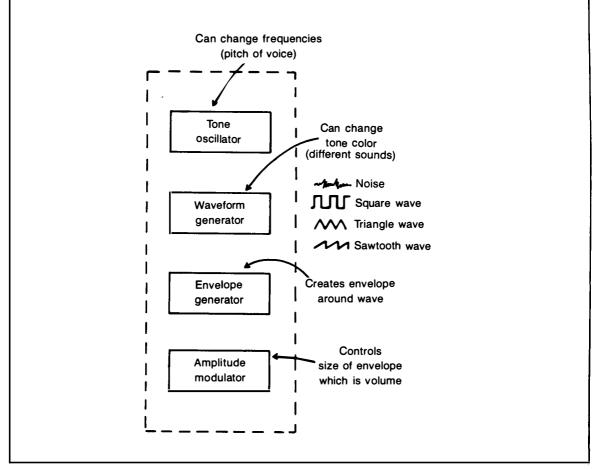

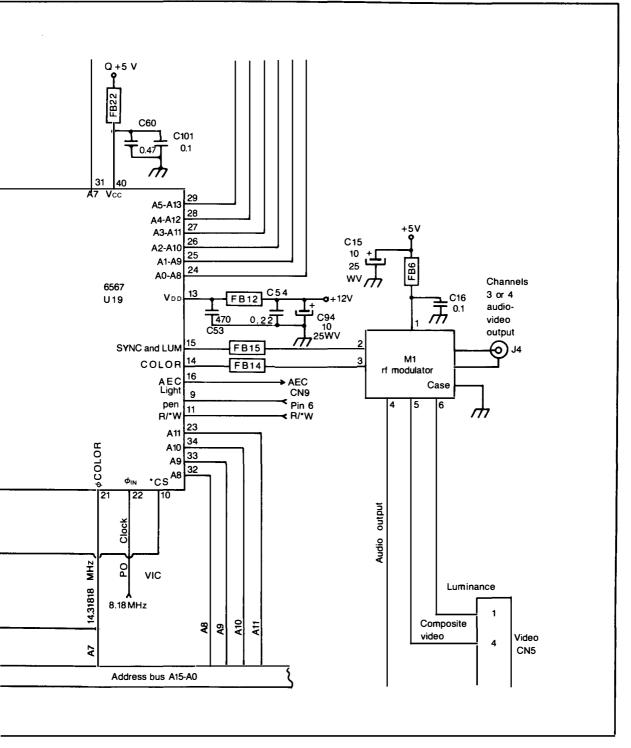

|   | 6510 Microprocessor 57<br>6526 Complex Interface Adapter 61<br>6567 Video Interface Chip 65<br>6581 Sound Interface Device 69                                                                                                                                                                                                                                   |     |

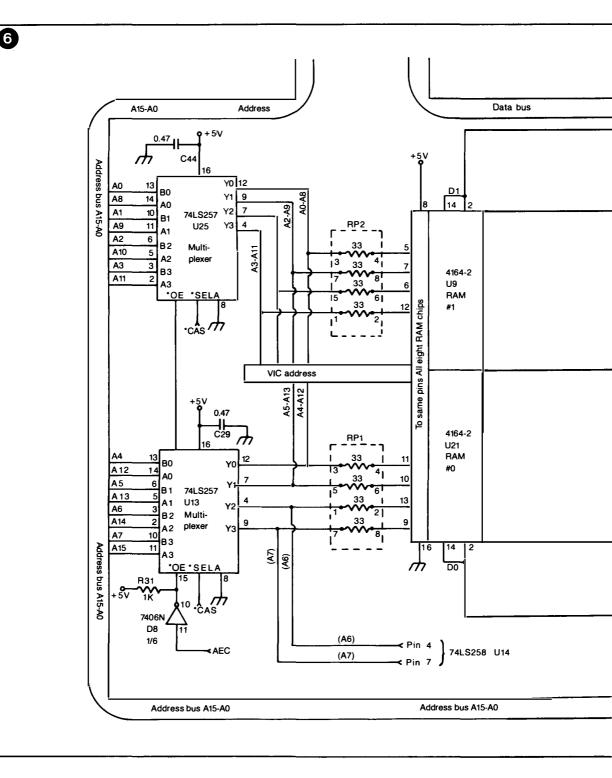

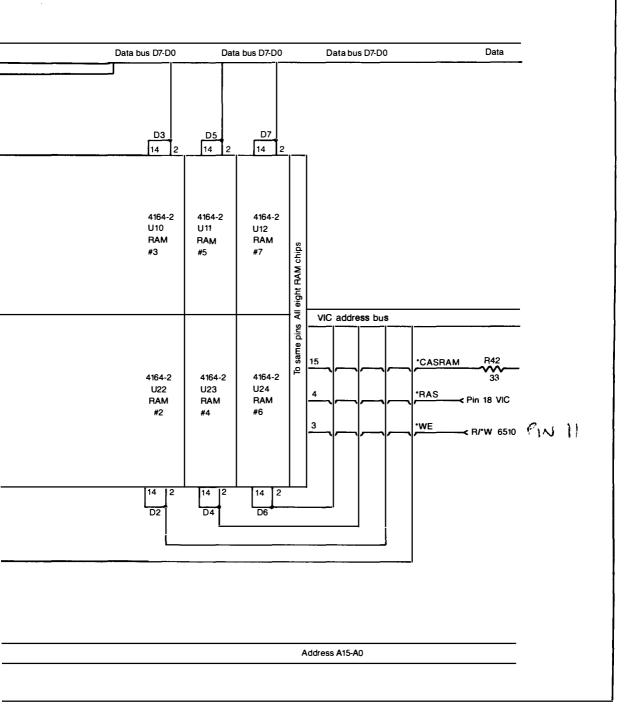

| 6 | Random Access Memory                                                                                                                                                                                                                                                                                                                                            | 73  |

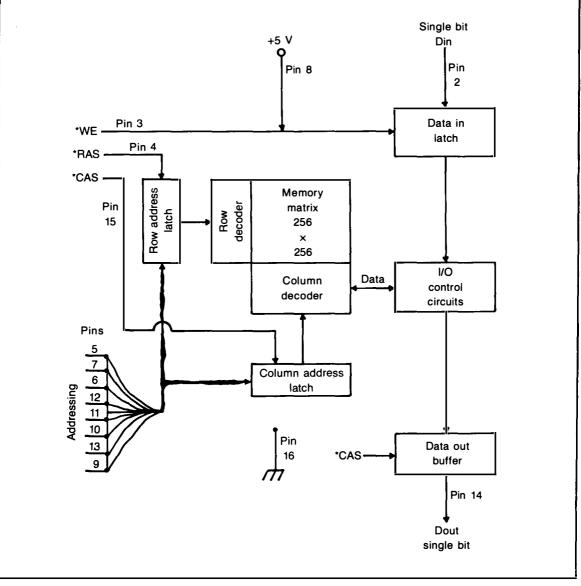

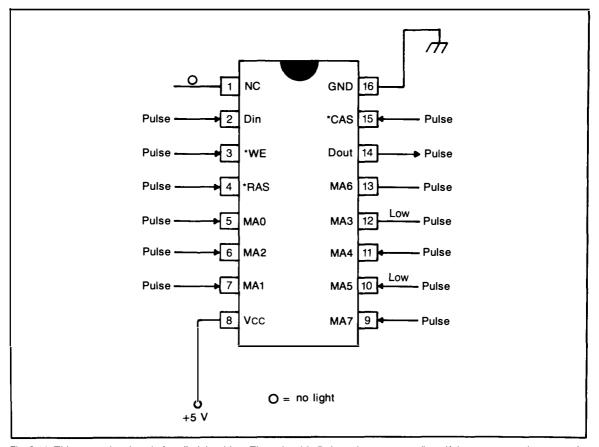

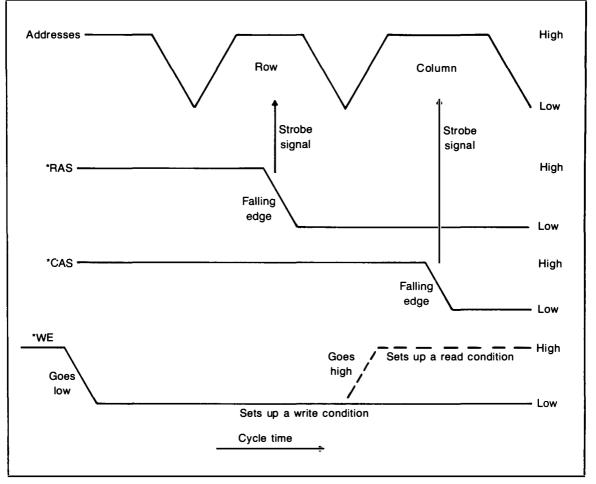

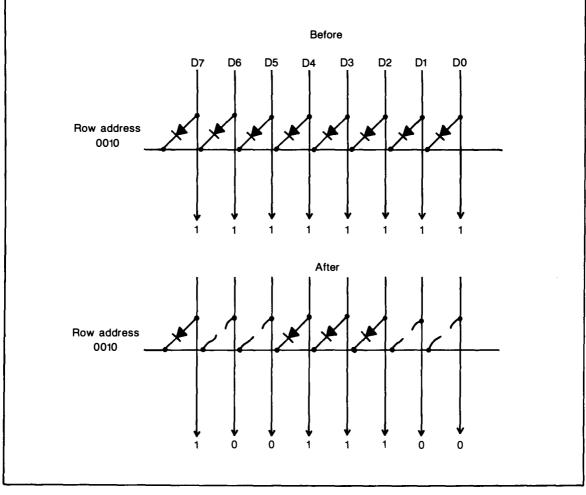

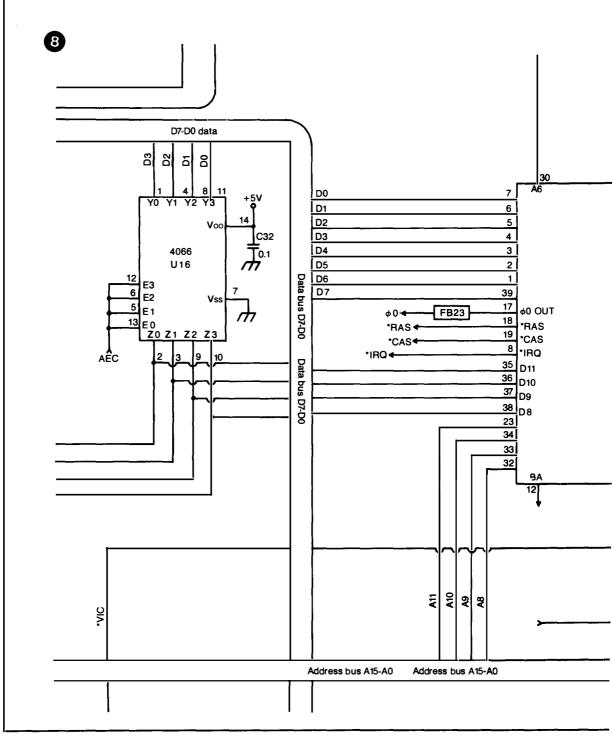

|   | Static RAM 74<br>Dynamic RAM 77<br>Memory Refresh—Memory Layout—Operation—Timing—Refresh Timing                                                                                                                                                                                                                                                                 |     |

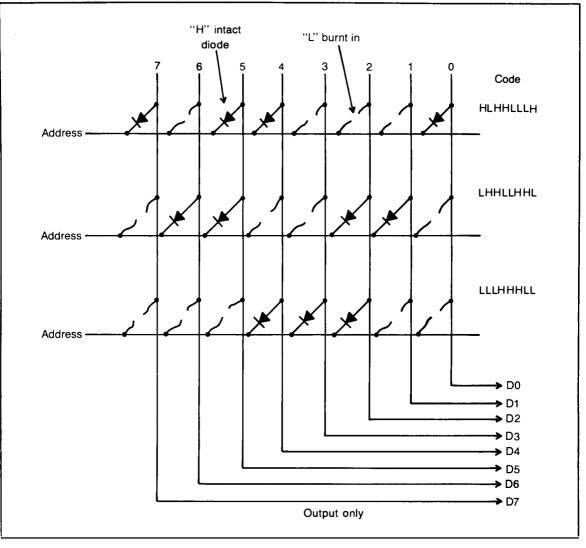

| 7 | Read Only Memory                                                                                                                                                                                                                                                                                                                                                | 90  |

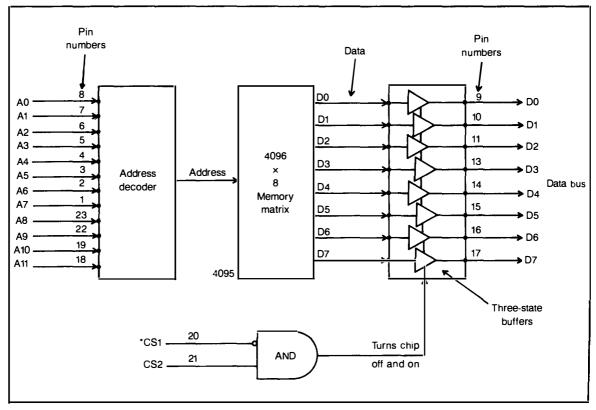

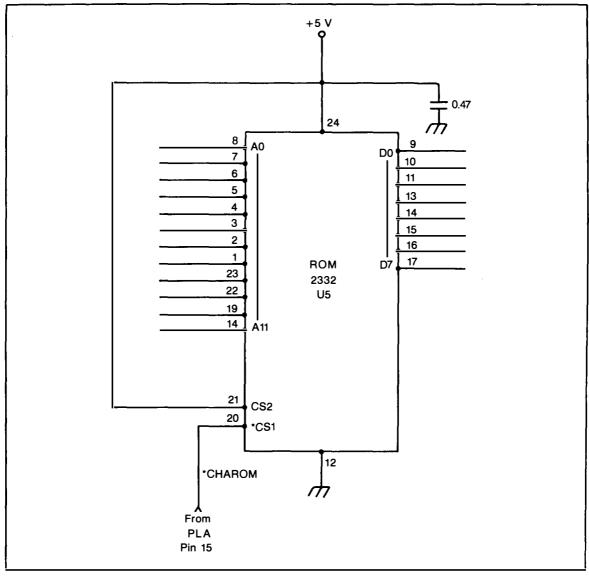

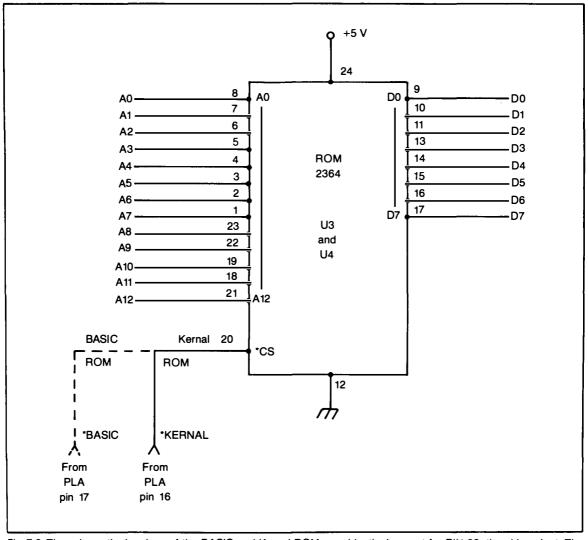

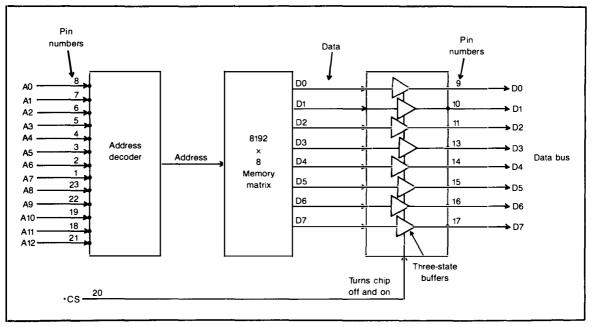

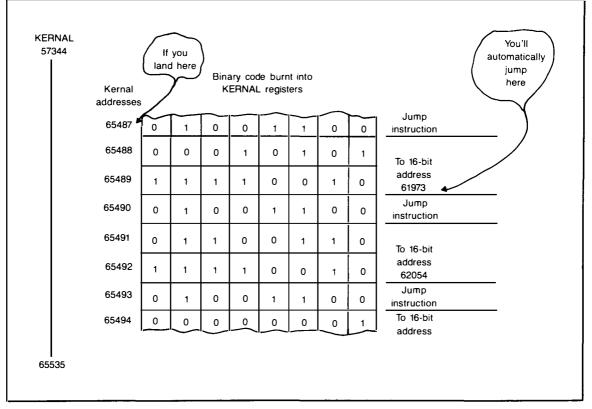

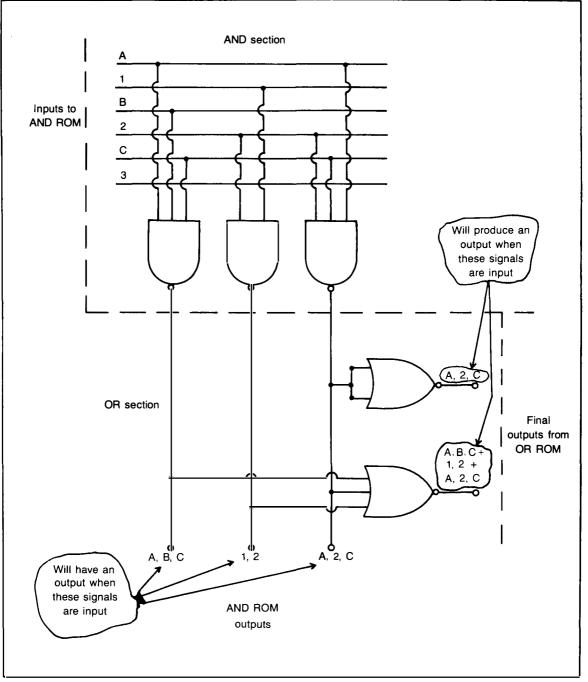

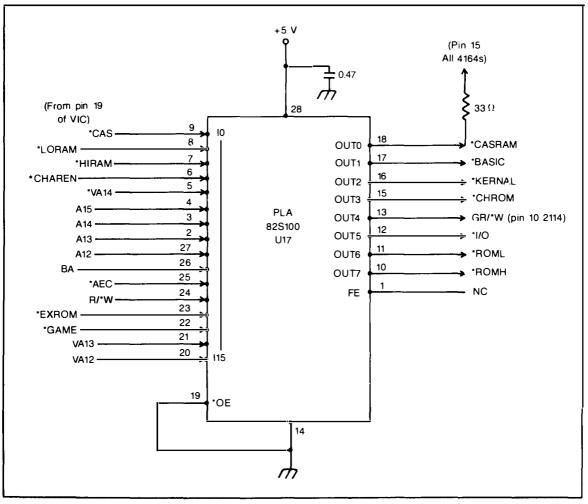

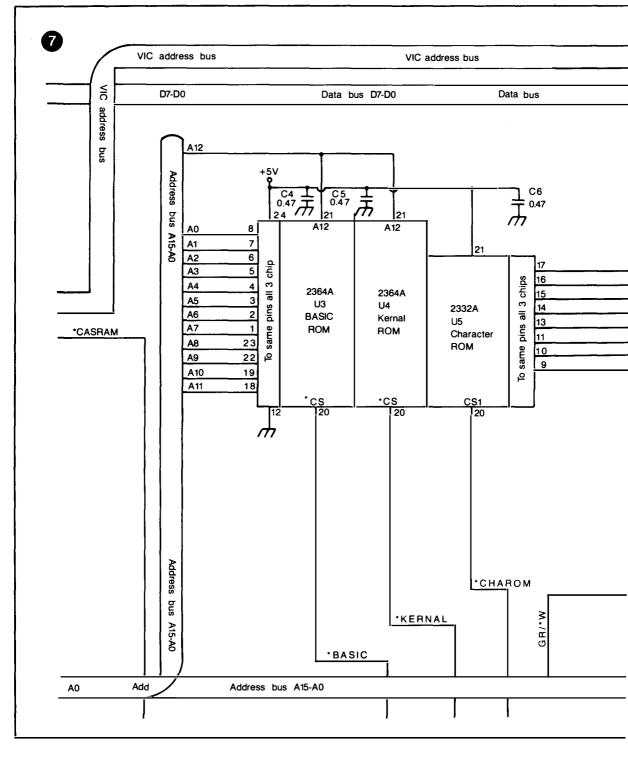

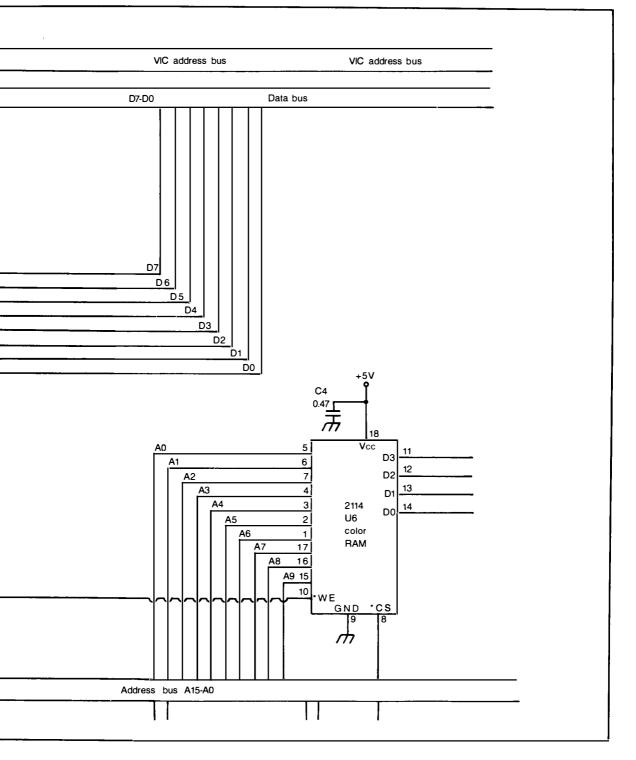

|   | Block Diagram 93<br>Character ROM 96<br>Kernal and BASIC ROM 97<br>BASIC ROM—Kernal ROM—Jump Tables<br>Programmable Logic Array 102<br>82S100 Pinout—PLA Inputs<br>Service Charts 107                                                                                                                                                                           |     |

| 8 | Other Integrated Circuits                                                                                                                                                                                                                                                                                                                                       | 109 |

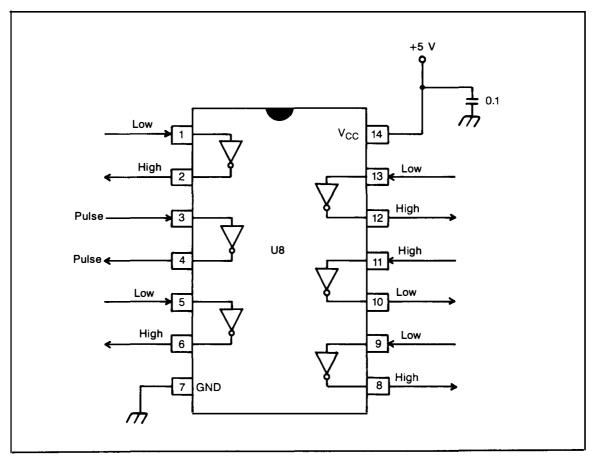

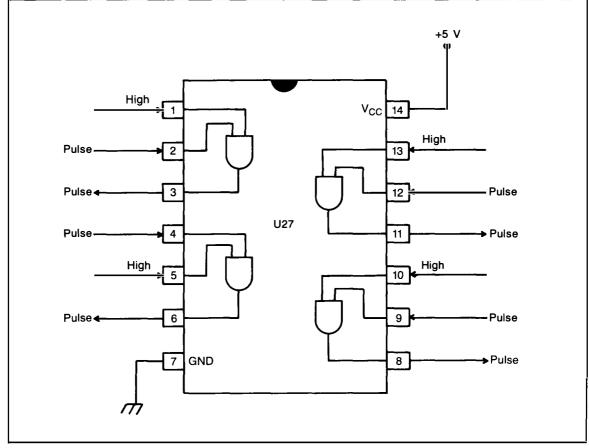

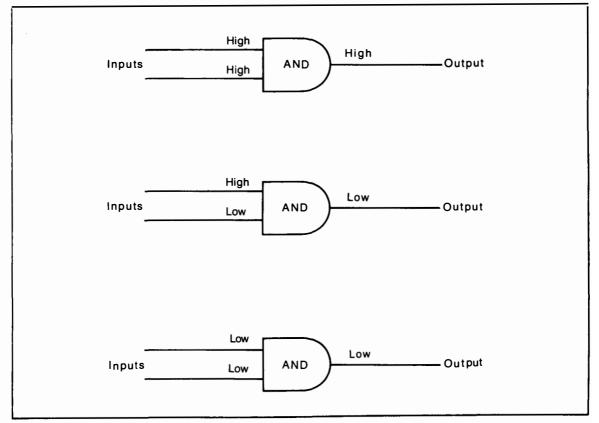

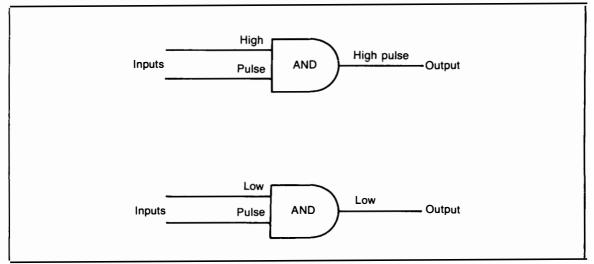

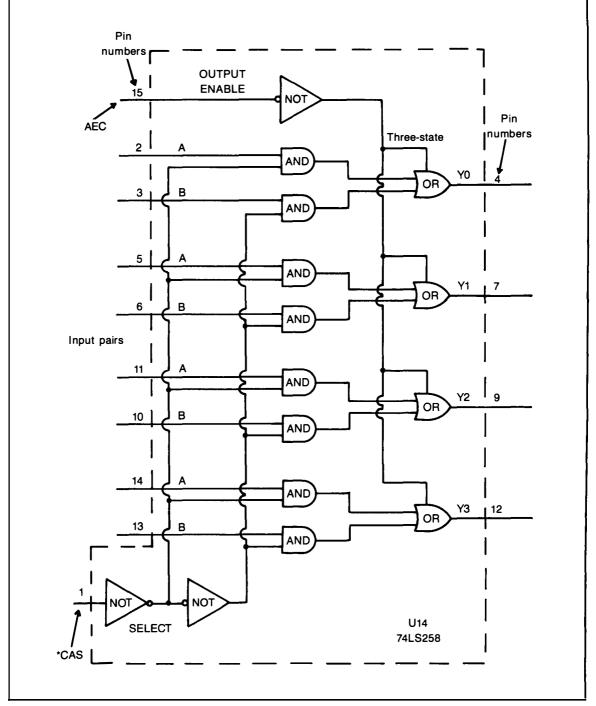

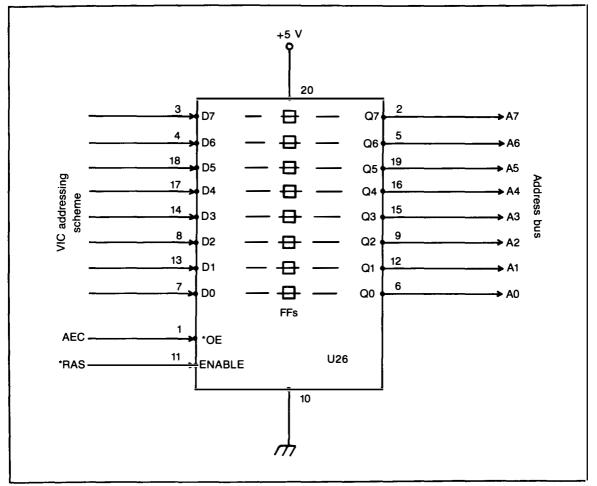

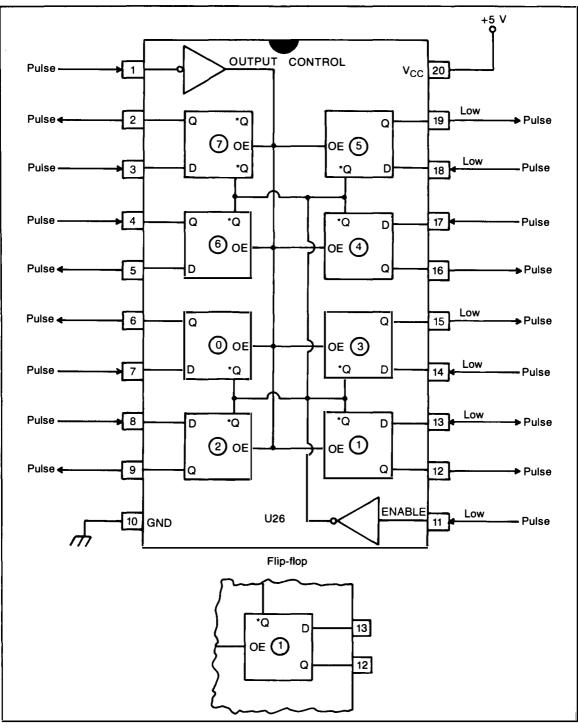

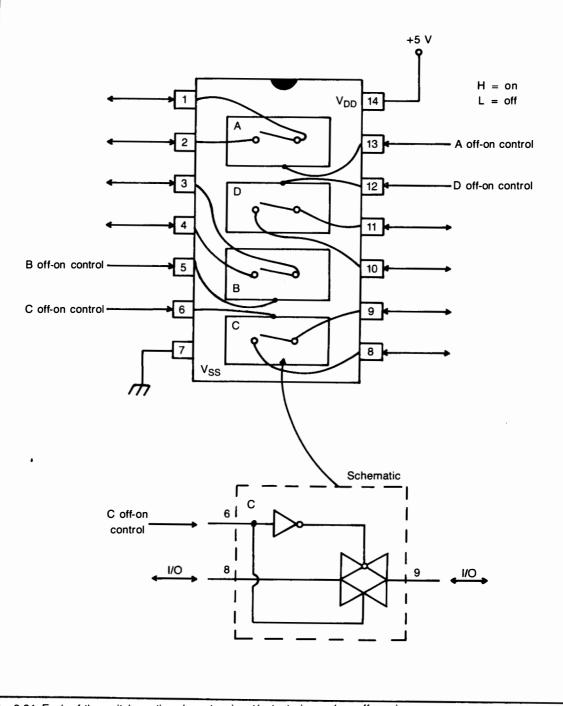

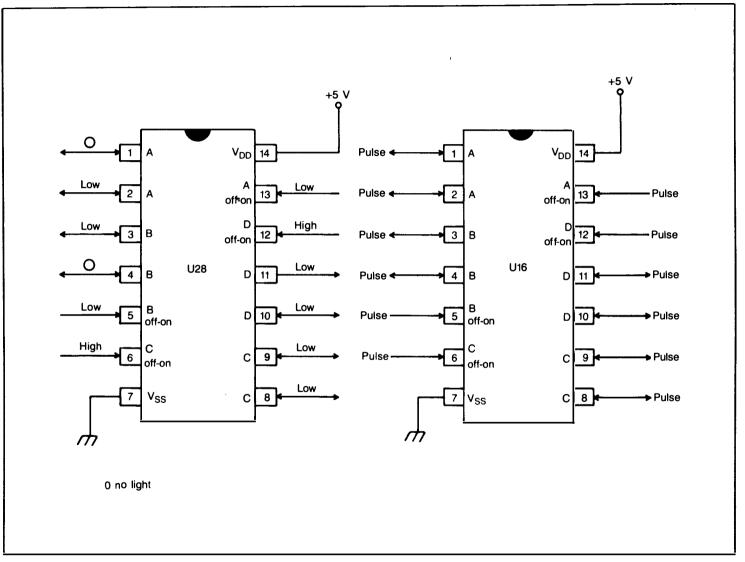

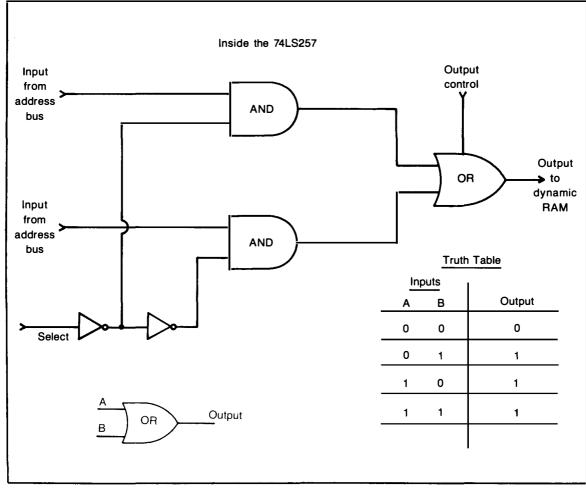

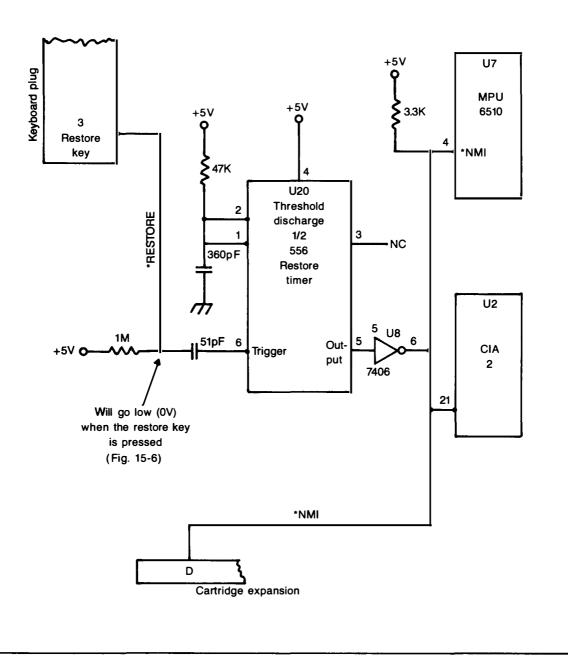

|   | 7406A Hex Inverter 109<br>74LS08 Quad 2-Input AND Gate 111<br>74LS74 Dual D Flip-Flop 114<br>74LS193 Up/Down Counter 116<br>74LS139 2-4 Decoder 118<br>74LS257 Quad 2-Input Multiplexer 121<br>74LS258 Quad 2-Input Multiplexer 122<br>74LS373 Octal D-Type Latch 126<br>4066 Quad Bilateral Switch 130<br>556 Dual Timer 131<br>Other Chip-like Components 136 |     |

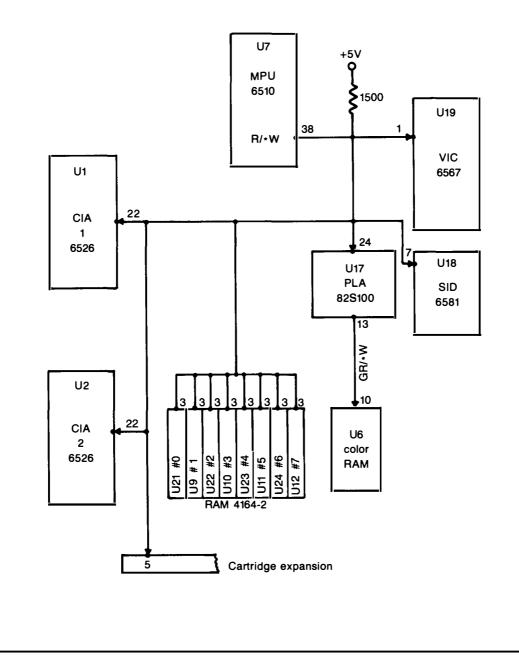

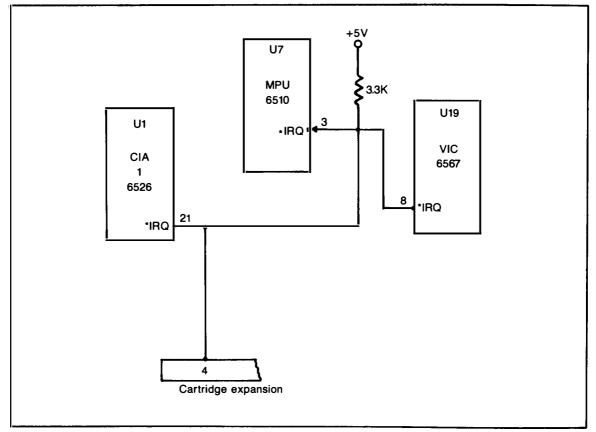

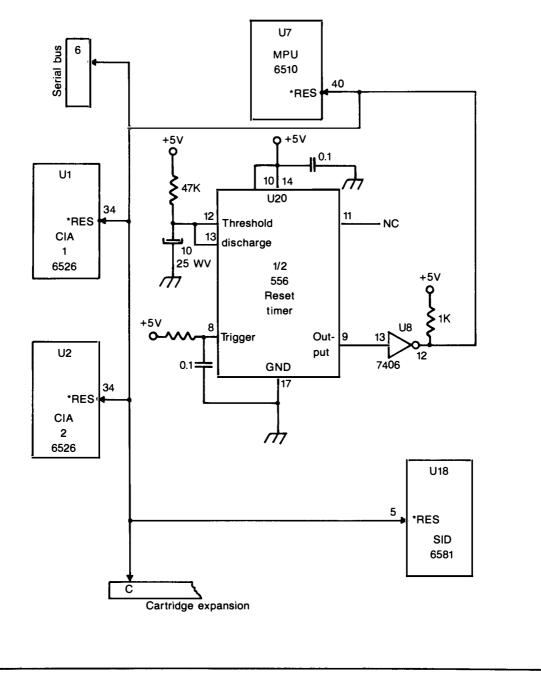

| 9 | System Block Diagram                                                                                                                                                                                                                                                                                                                                            | 138 |

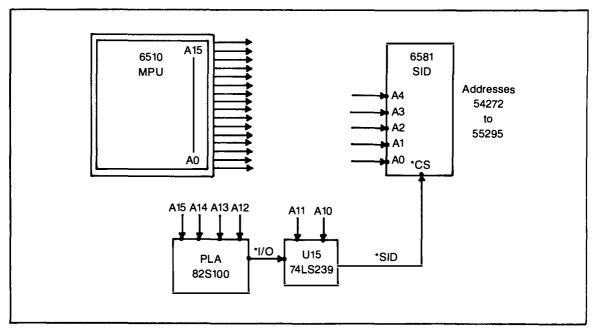

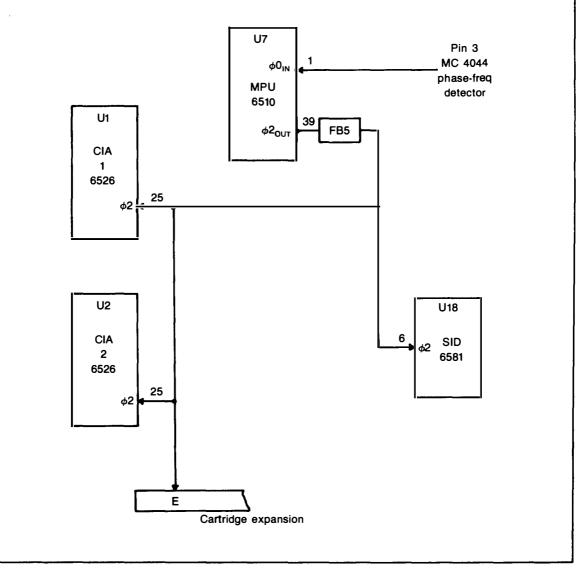

|   | Block Diagram 138<br>MPU and Dynamic RAM 140<br>MPU and ROM 143<br>MPU and CIA Interface 143<br>MPU and VIC II 147<br>MPU and SID 151                                                                                                                                                                                                                           |     |

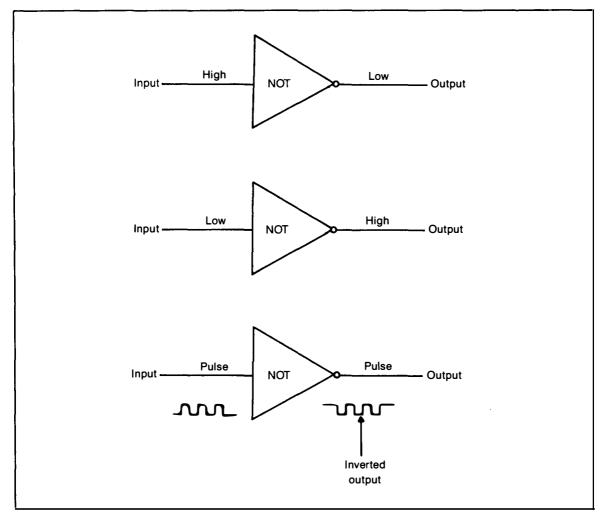

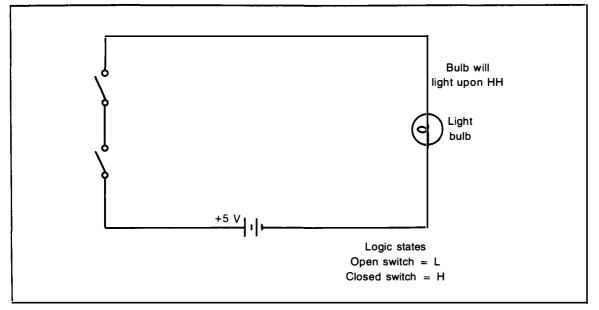

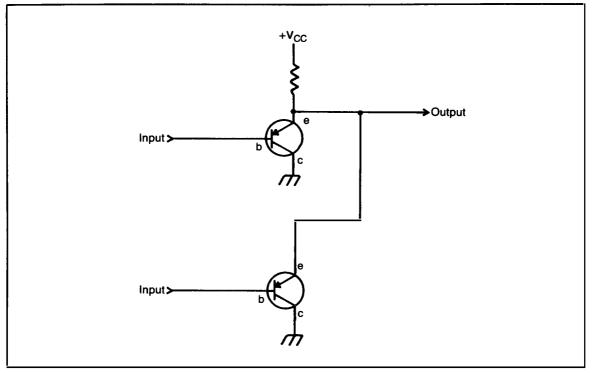

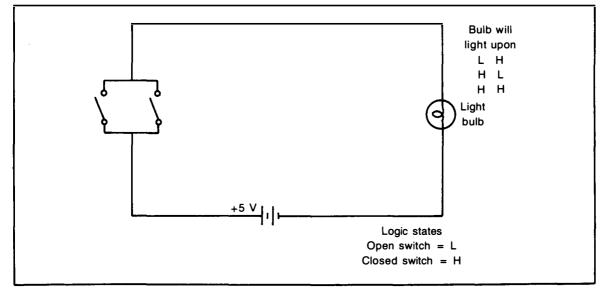

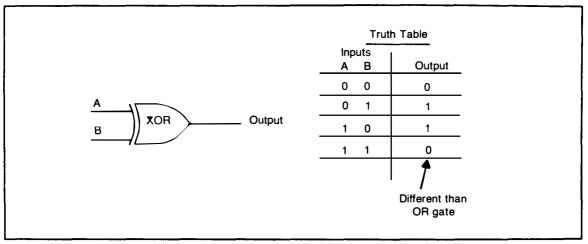

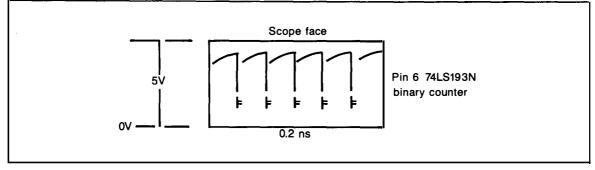

# 10 Servicing Logic Gates

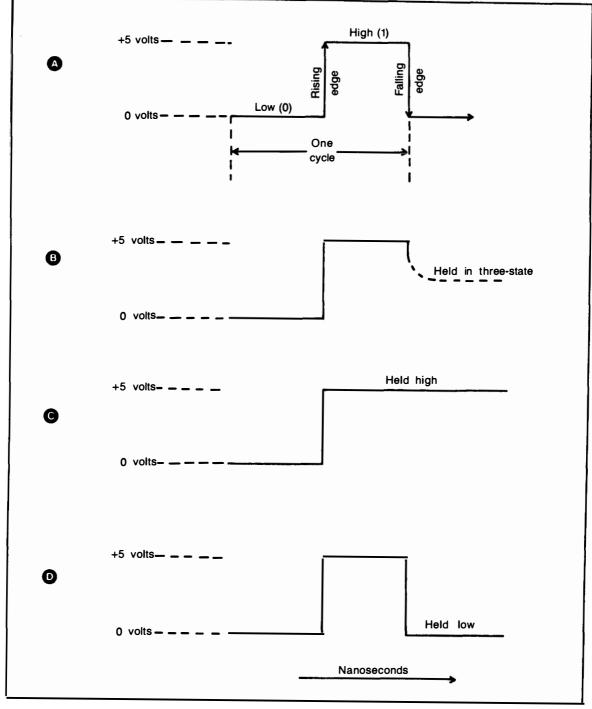

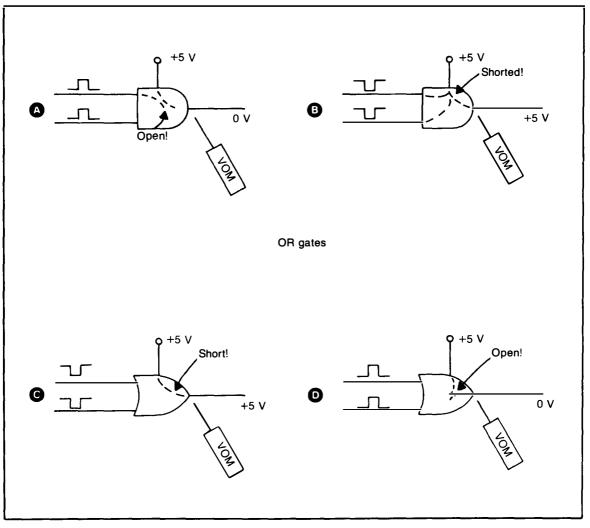

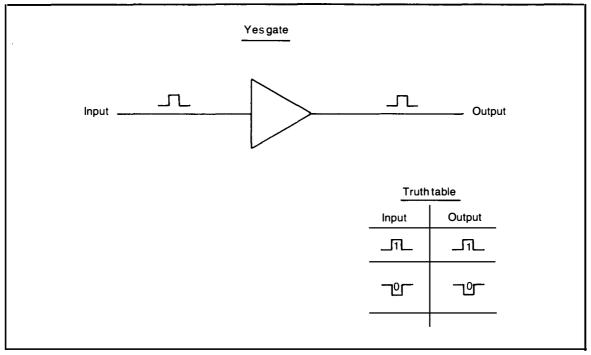

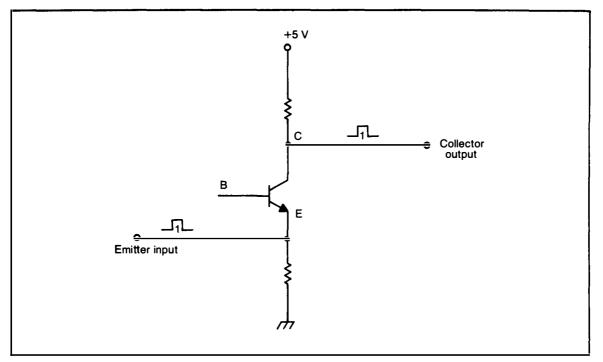

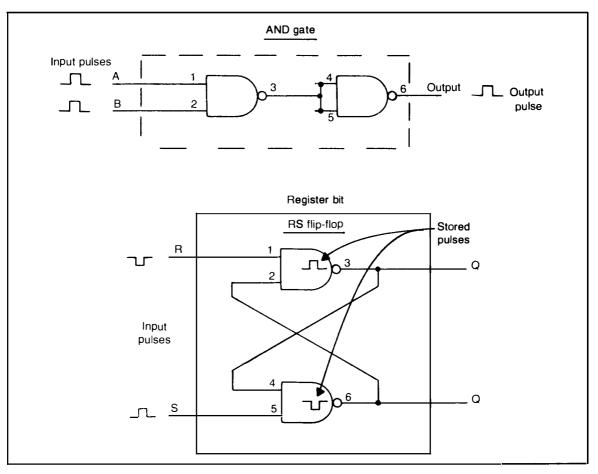

Decimal and Binary 153 Hexadecimal 156 PEEK and POKE 158 Gates 158 YES Gate—NOT Gate—AND Gate—OR Gate—XOR Gate—NOR and XNOR Gates Gate Testing Technique 172

## **11 Servicing Digital Registers**

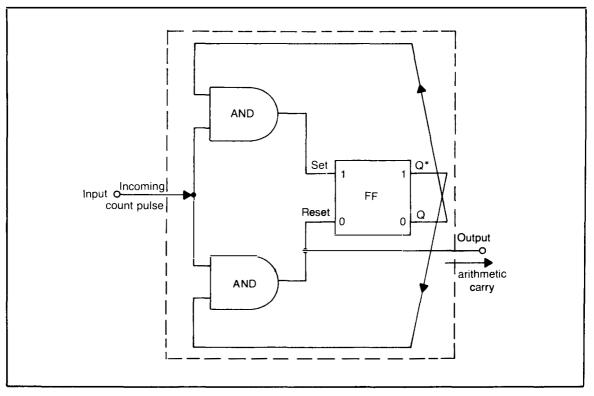

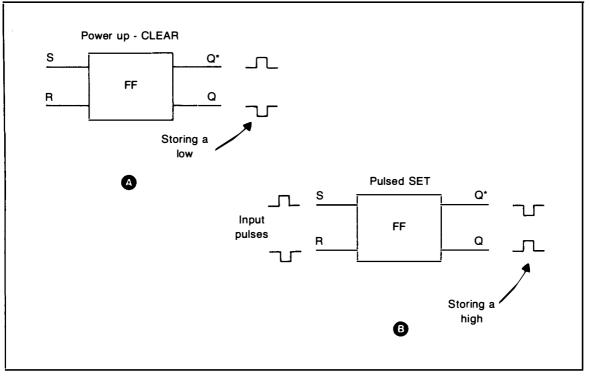

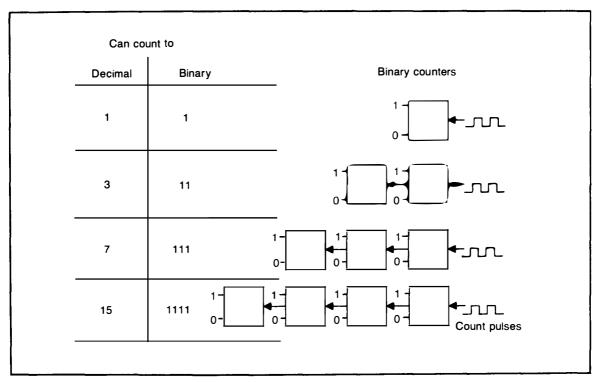

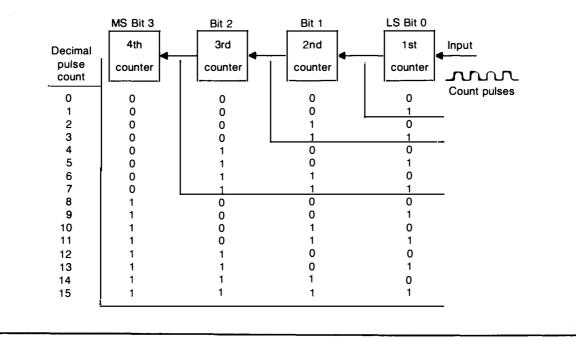

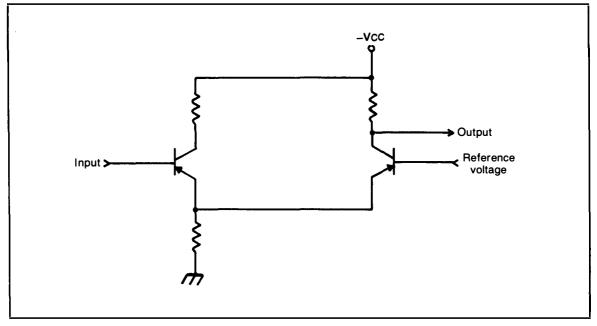

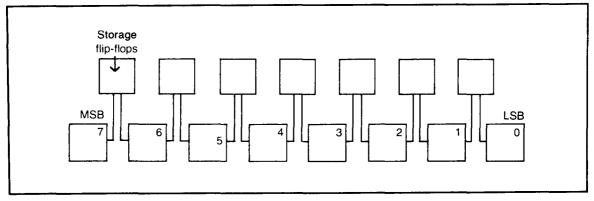

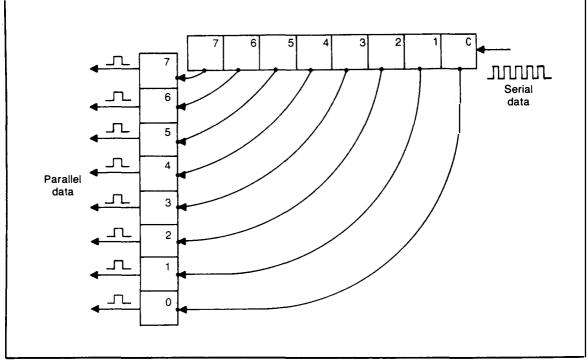

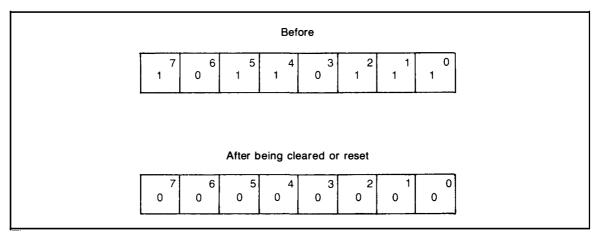

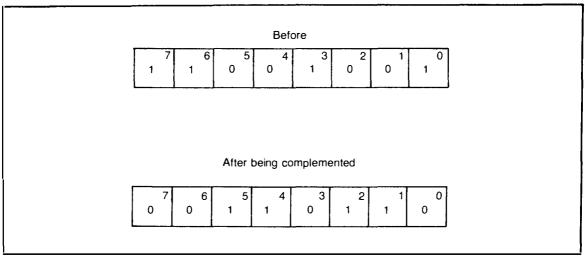

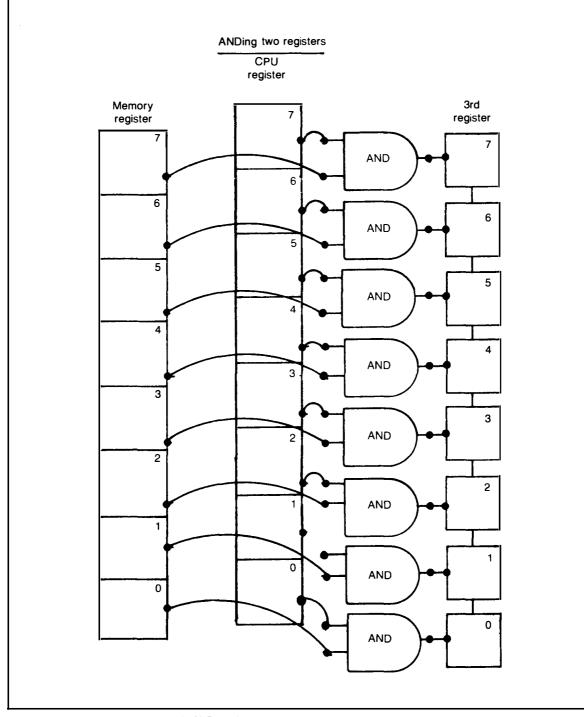

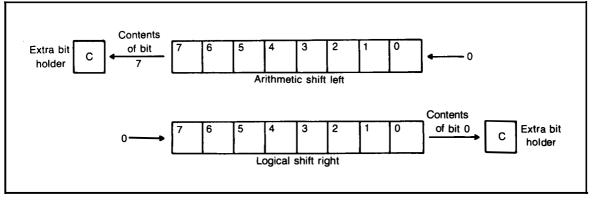

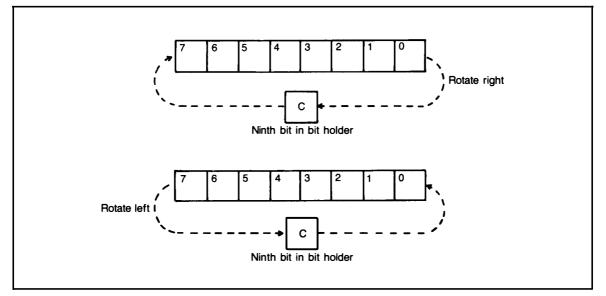

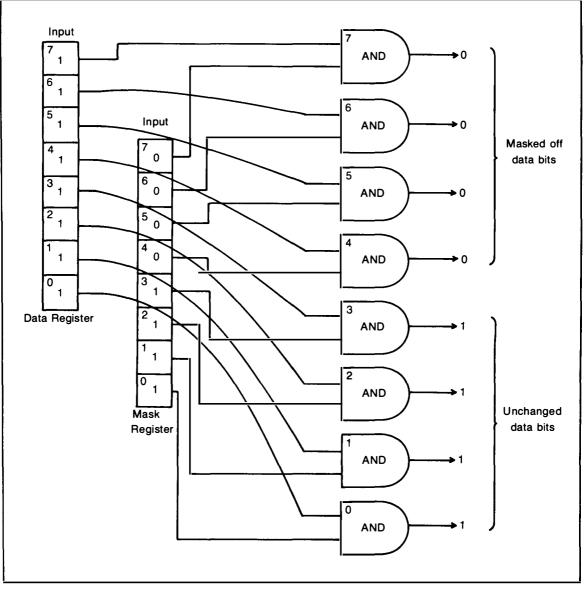

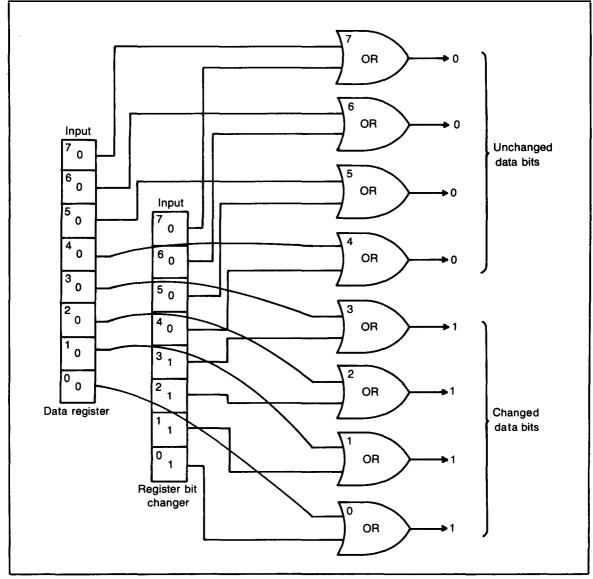

Flip-Flops 174 74LS74 D Flip-Flop—74LS373 D Latch—74LS193 Up/Down Counter—556 Dual Timer Computing Registers 183 Shifting—Clearing—Complementing—Increment, Decrement, and Jump—ANDing and ORing

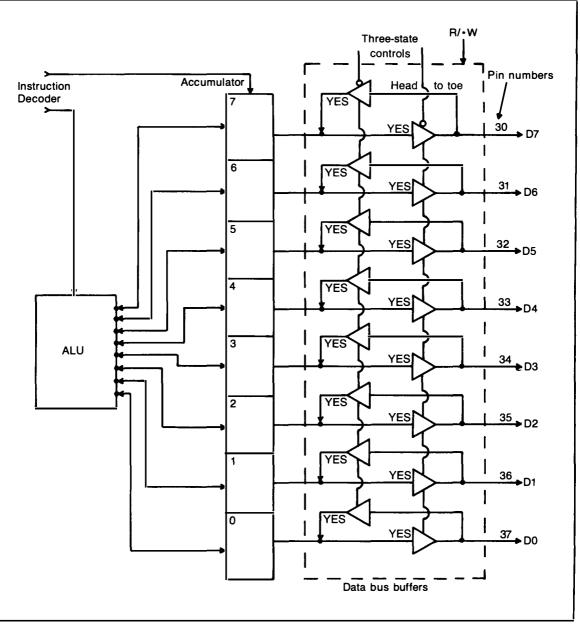

#### 12 6510 Microprocessor

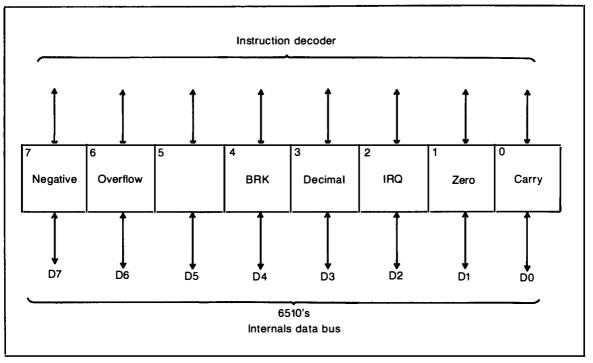

Addressing 192 Stack 194 Arithmetic Logic Unit 195 Shifting—Logic Manipulations Accumulator 200 Instruction Set 202 Instruction Byte—Fetch and Execute Index Register 206 Flag Register 207 Interrupts 209 Vector Addresses 211 Other Pins 211 Testing 211

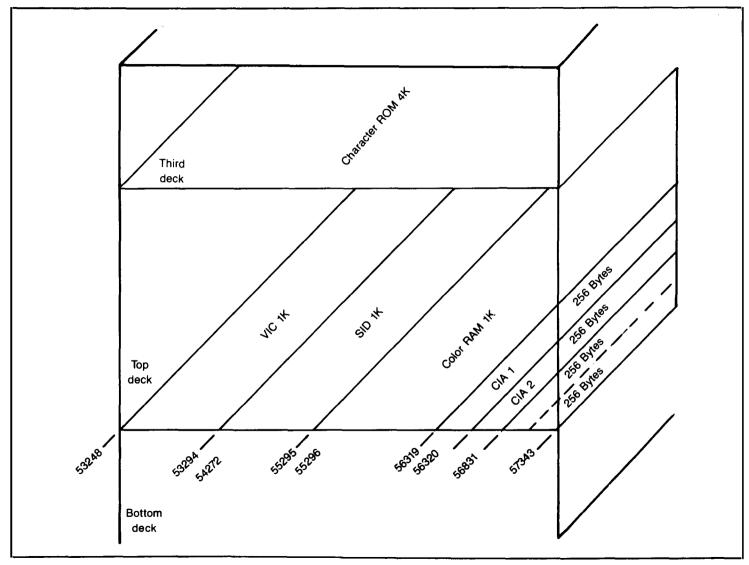

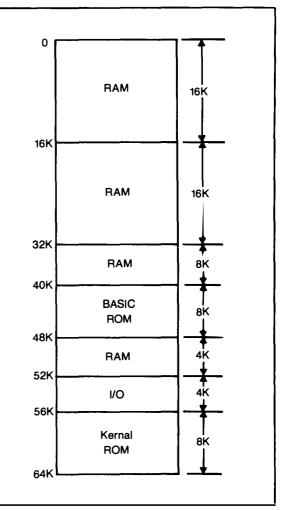

#### 13 Memory Maps

6510 I/O Port 214 Default Map 217 I/O Signals 217 Memory Decks 218 Reading and Writing to the Decks 221 Other Possible Maps 222 PEEKing and POKEing the Map 223

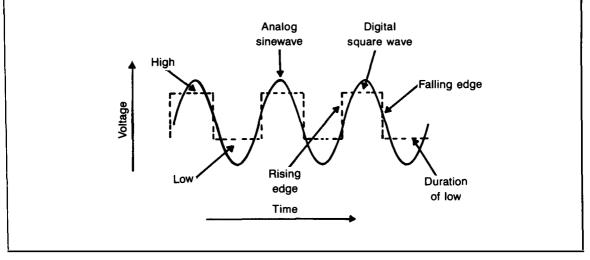

#### 14 Clock

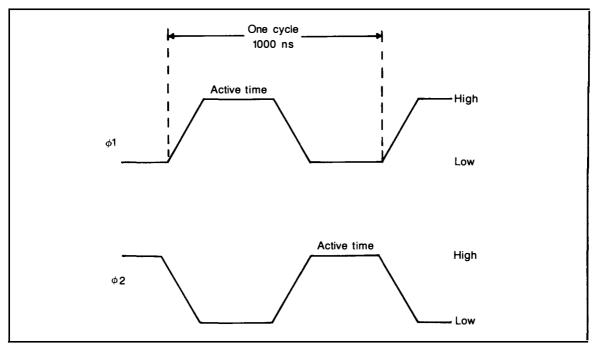

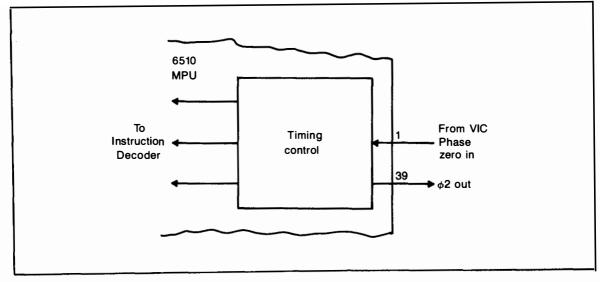

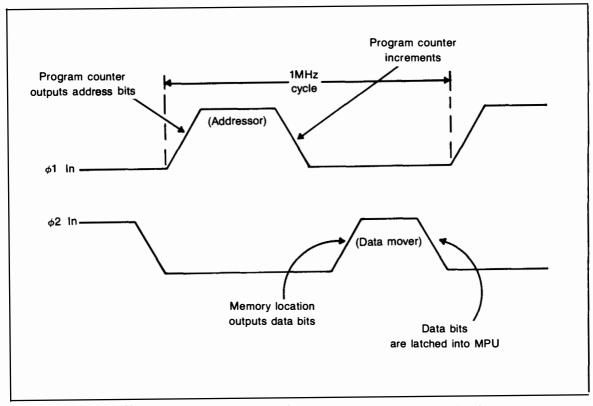

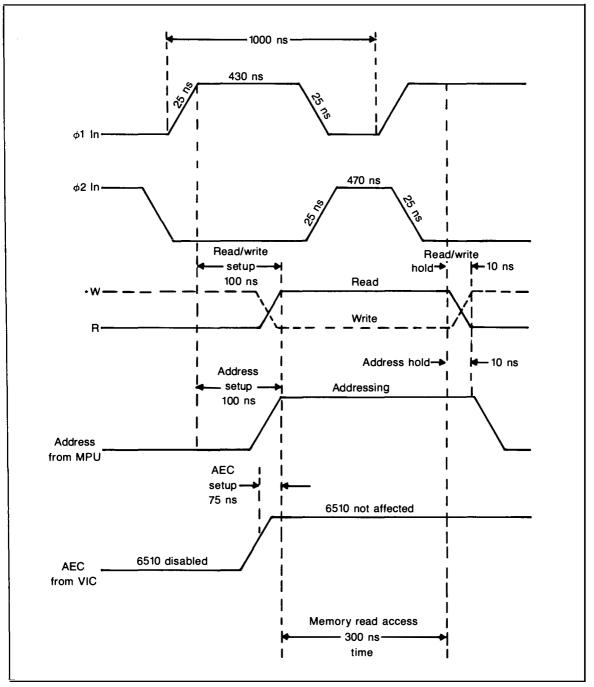

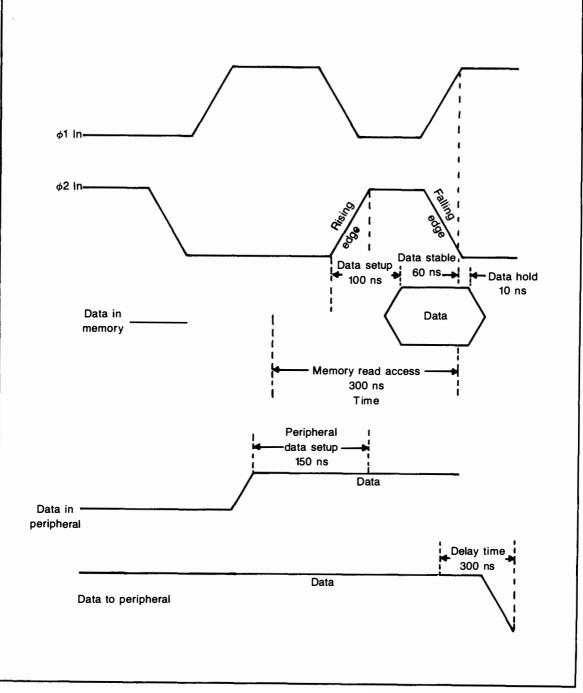

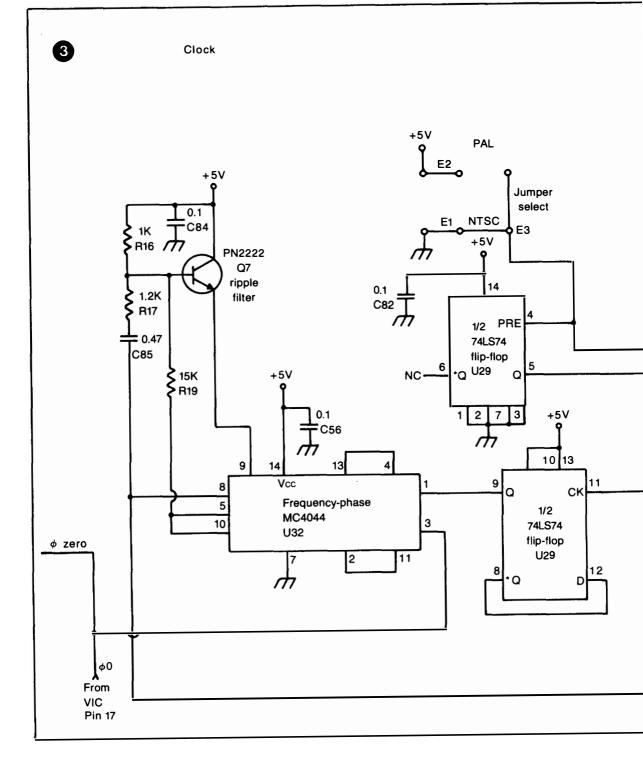

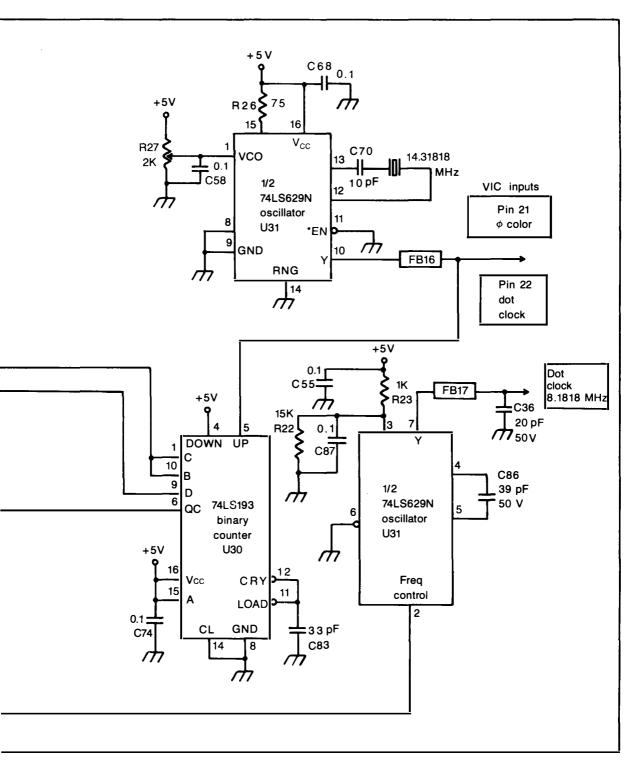

Sine Wave to Square Wave 224 Working Frequency 225 6510 Timing Control 228 Other Timing Signals 230 Address Signals—Data Timing—Reading and Writing to Peripherals Testing the Clock 233

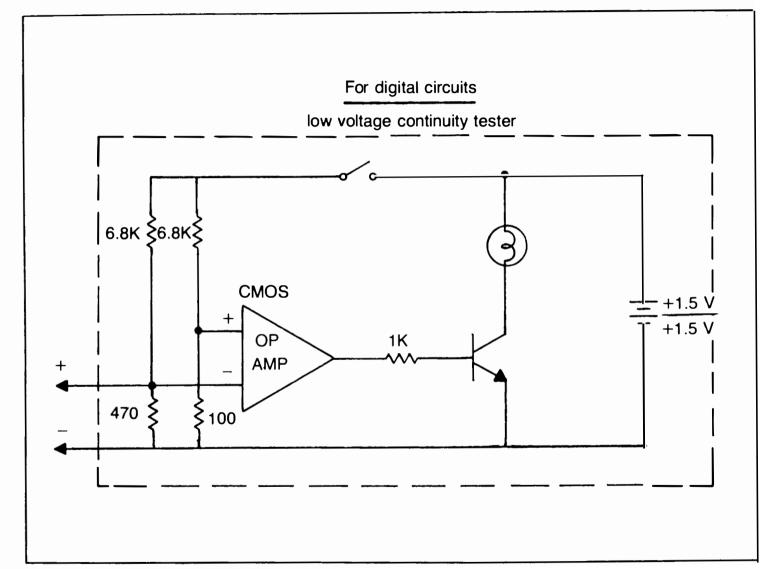

# 15 Address, Data, and Control Buses

Address Bus 236 Address Assignments—Address Bus Connections Data Bus 239 Control Lines 241 R/\*W Line—\*IRQ Line—Reset Line— $\phi$ 0 and  $\phi$ 2 Signals Testing the Bus Lines 242 Using the Tester—PEEK and POKE Tests—Control Line Tests

# 16 Complex Interface Adapters

Addressing and Controlling 253

174

192

214

236

253

224

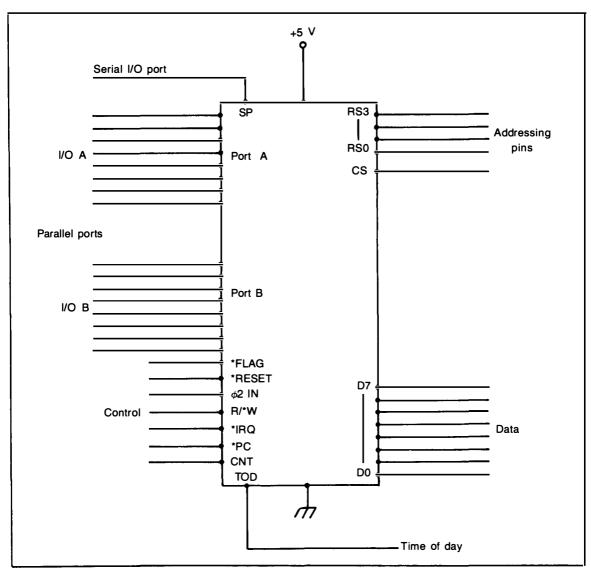

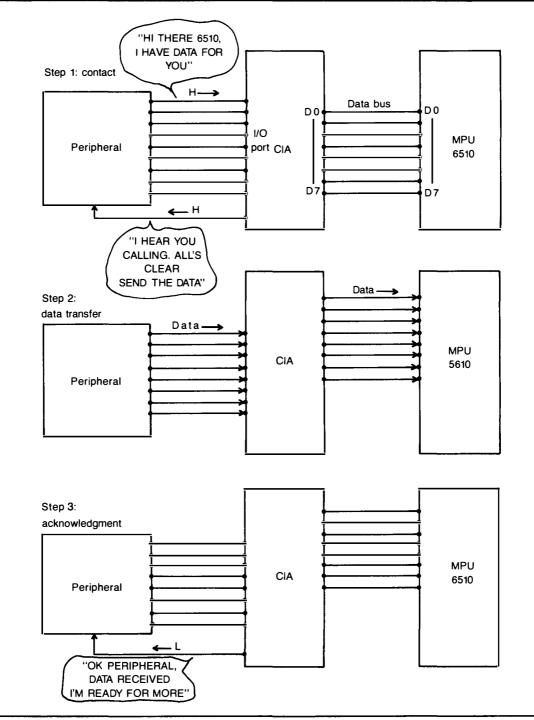

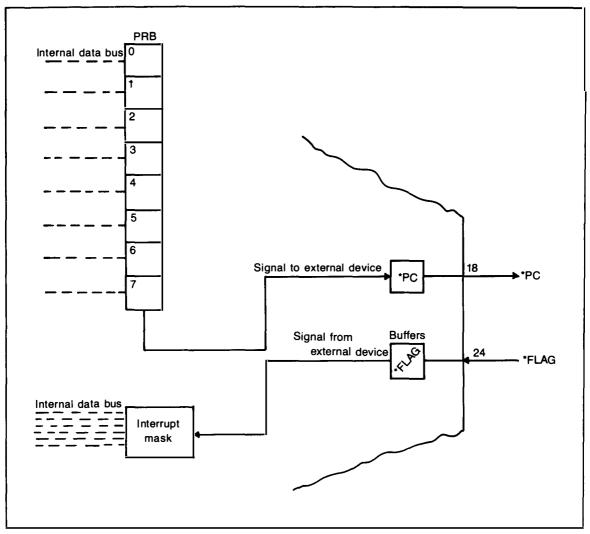

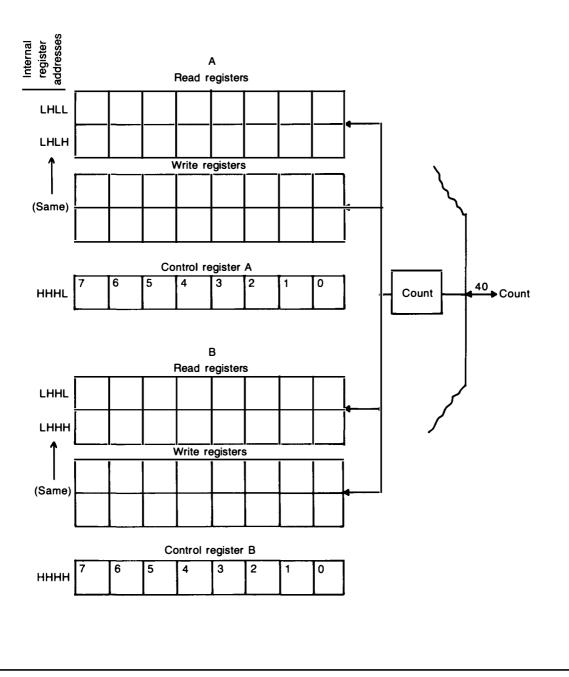

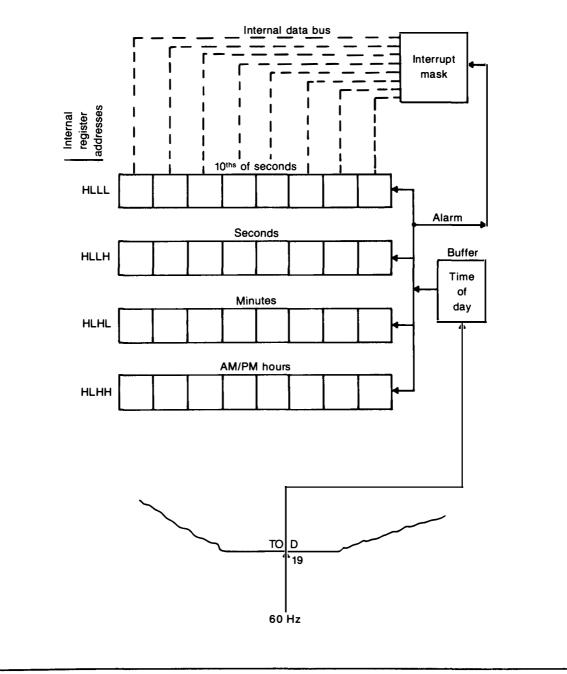

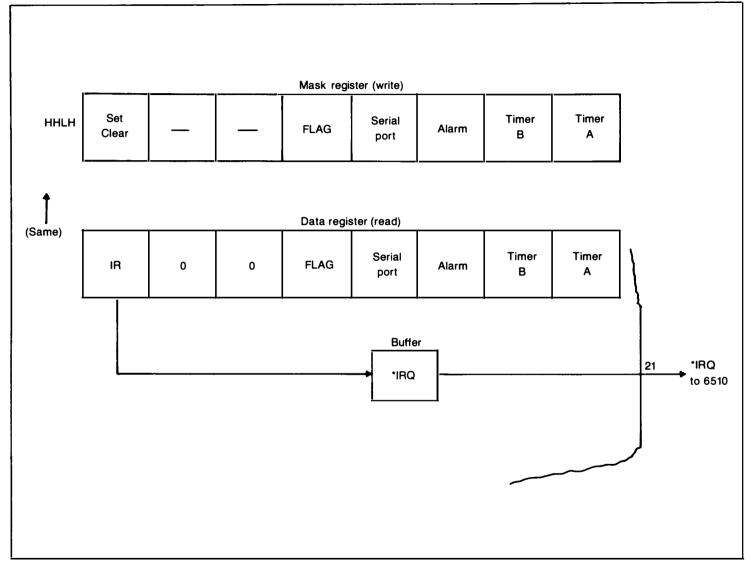

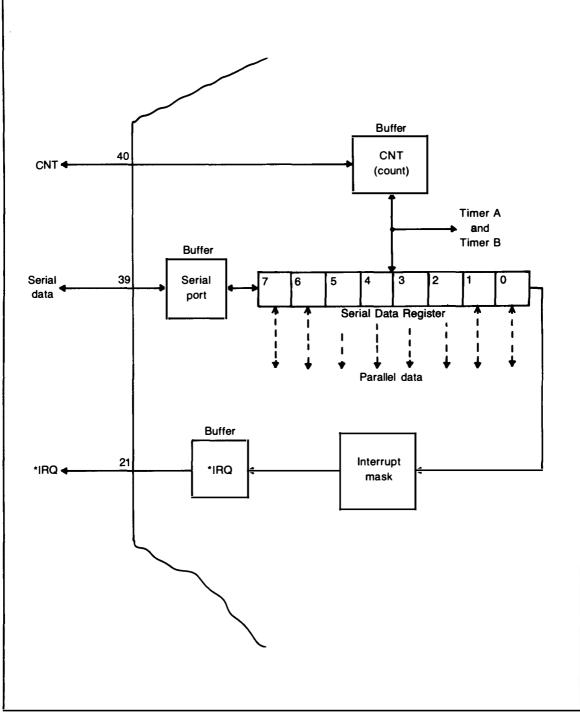

Internal Data Transfer 255 Timing 255 Write Timing—Read Timing I/O Ports 257 \*PC and \*Flag Pins 259 Timers 259 Real Time Clock 259 Interrupt Control Register 262 Serial Data Register 265 Operation 265 CIA1—CIA2 Testing 268

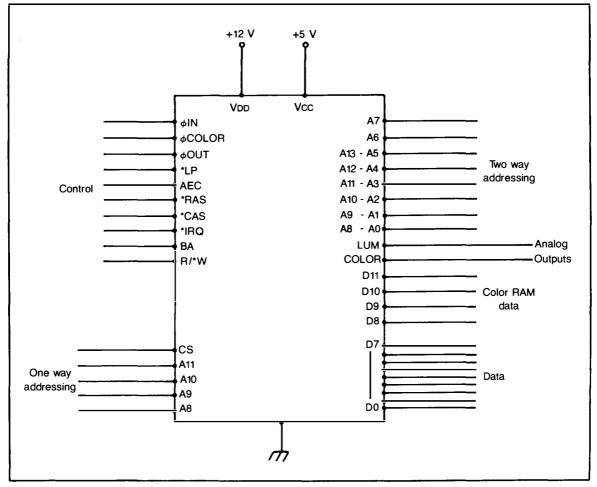

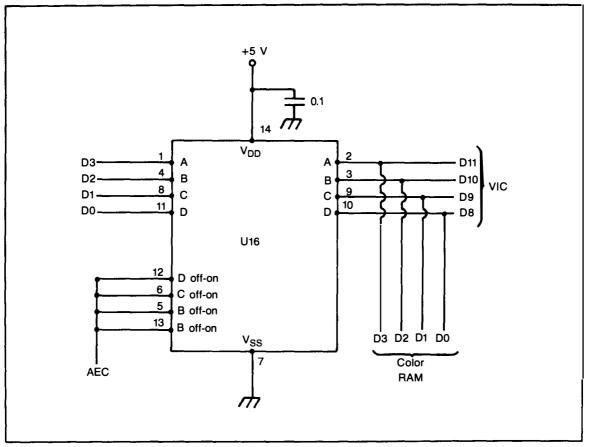

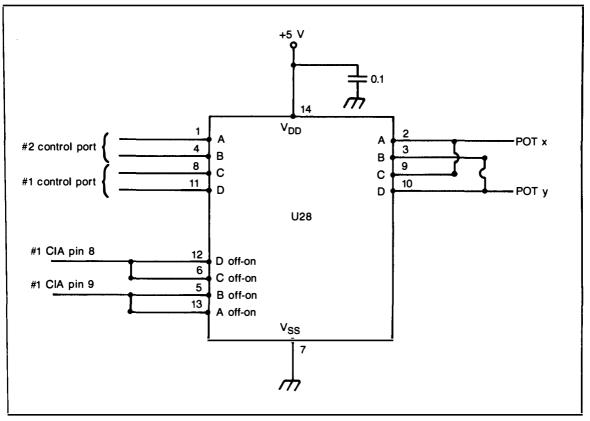

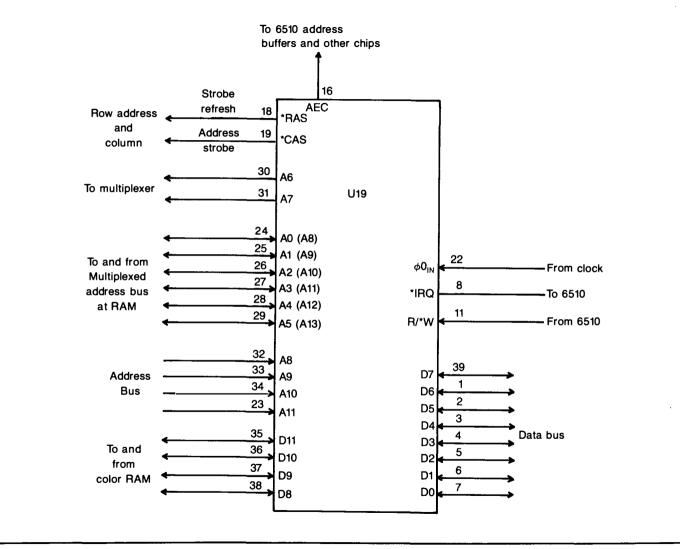

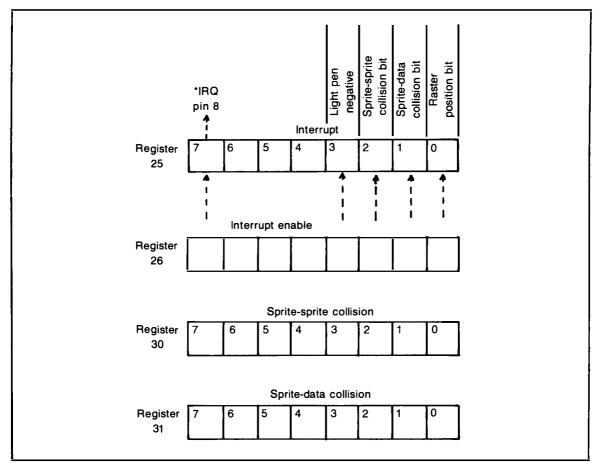

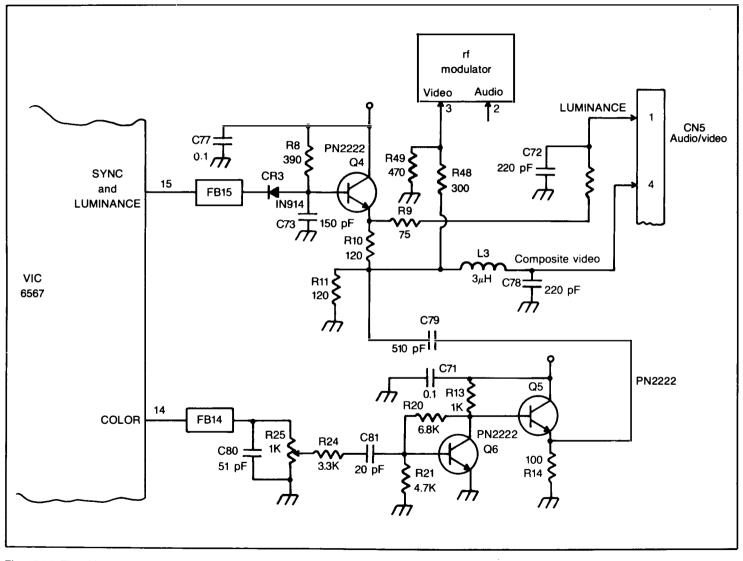

### 17 Video Interface Chip

Operation 269 Special Address Lines 271 Data Bus Connections 271 Modes 275 Displaying Characters—Character Fetch—Character Color—Character Modes—Bit Map Modes Sprites 280 Other VIC Features 283 Raster Register—Interrupt Register Light Pen 285 Video Output 286 Testing 289

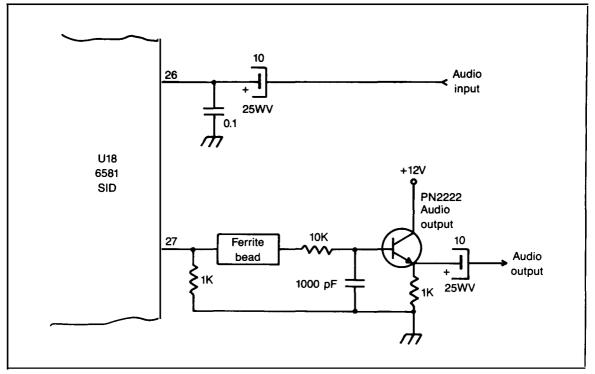

## **18 Sound Interface Device**

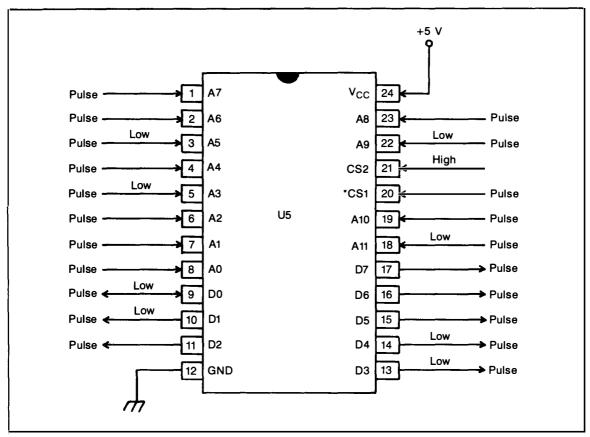

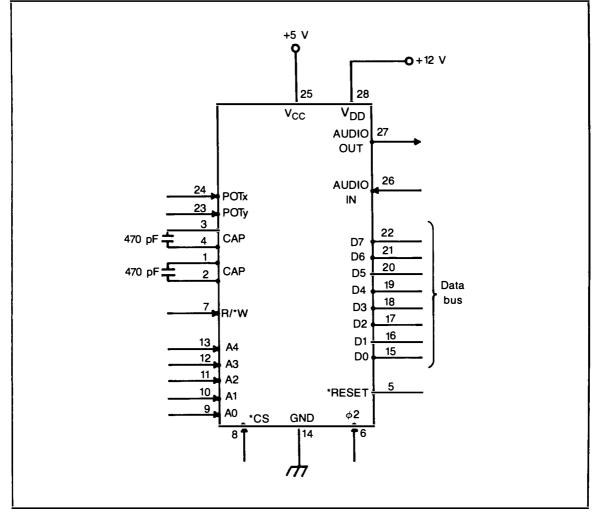

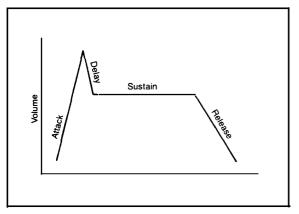

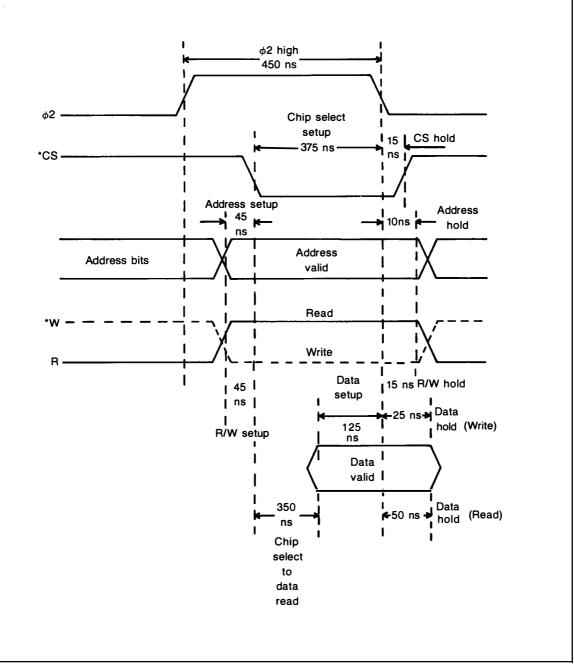

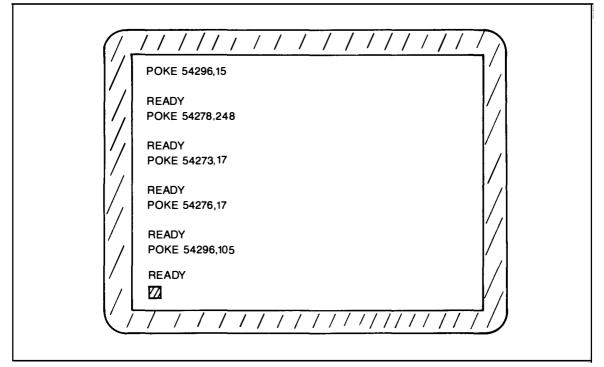

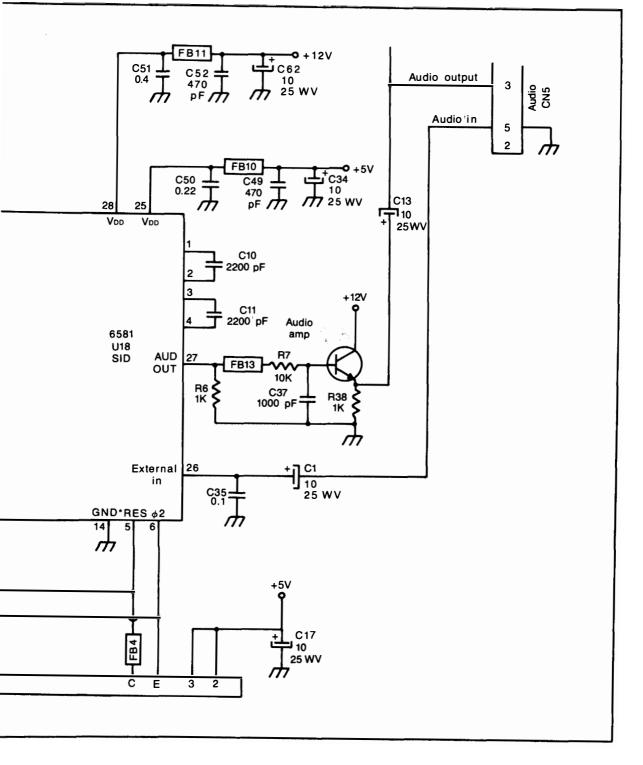

Pinout 290 Special Inputs 291 Operation 291 Registers 295 First Voice Registers—Voice Control Register—Envelope Generator Register—Other Voices—Filter Registers—Mode/Volume Register—Writing and Reading—Pot Registers—Osc 3/Random Register—Env 3 Register Timing 303 Testing 303

# 19 Inputs and Outputs

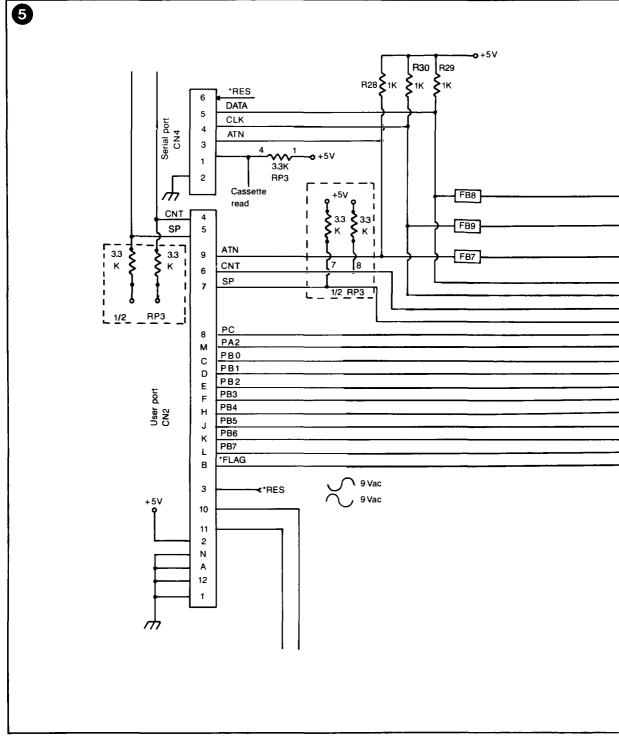

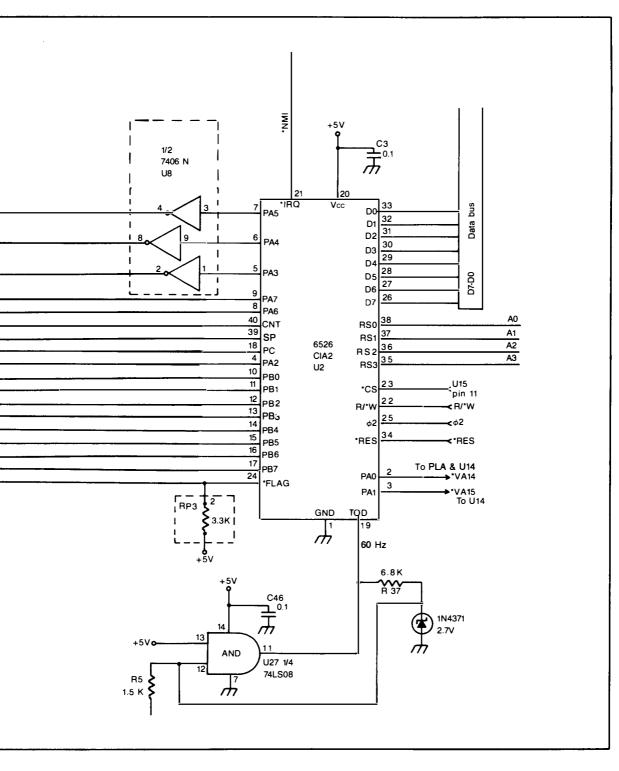

Control Ports 306 Expansion Ports 306 Audio-Video Ports 309 Serial I/O Ports 309 Cassette I/O Slot 311 User Connector 312

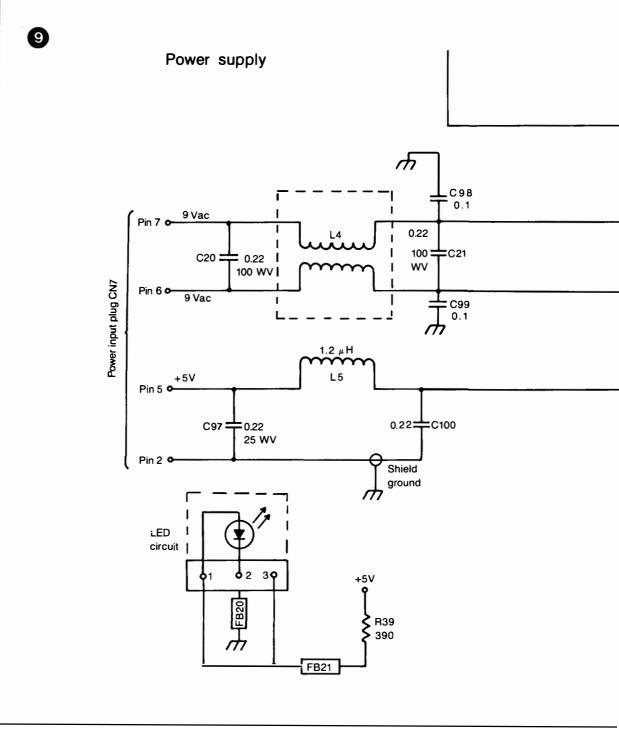

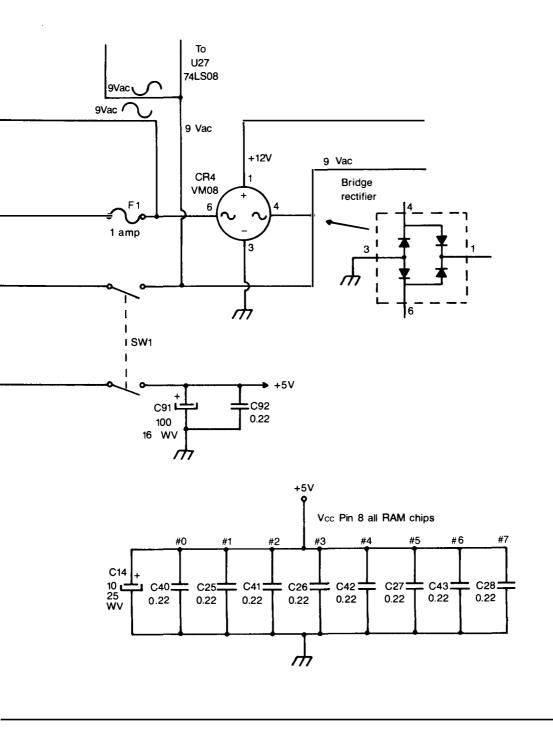

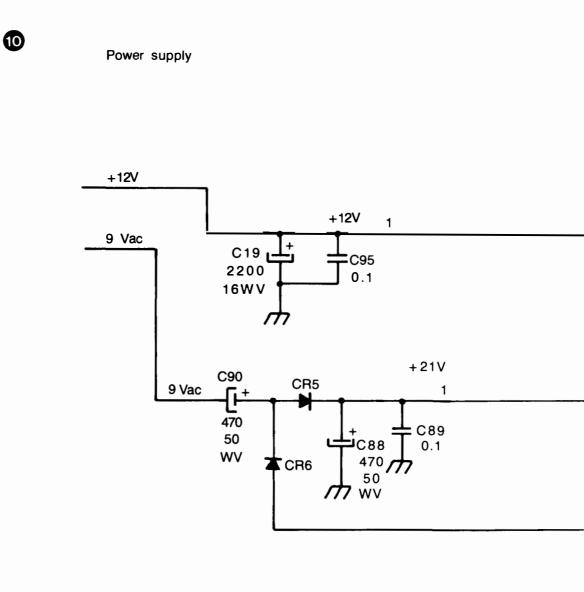

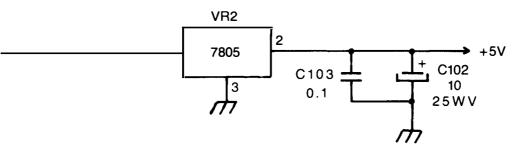

## 20 Power Supply

Trouble Locations 313 Fuse Considerations 316 Source Checking 316 The Main Line 317

# Appendix Master Schematic

## Index

269

290

305

319

313

349

#### **Test Point Charts**

| Figure #  | Chip #  | Chip Job            |

|-----------|---------|---------------------|

| 6-4       | 2114    | Color RAM           |

| 6-14      | 4164    | Dynamic RAM         |

| 7-3       | 2332    | Character ROM       |

| 7-8       | 2364    | Basic ROM           |

|           |         | Kernal ROM          |

| 7-12      | 82S100  | PLA                 |

| 8-1       | 7406    | Hex Inverter        |

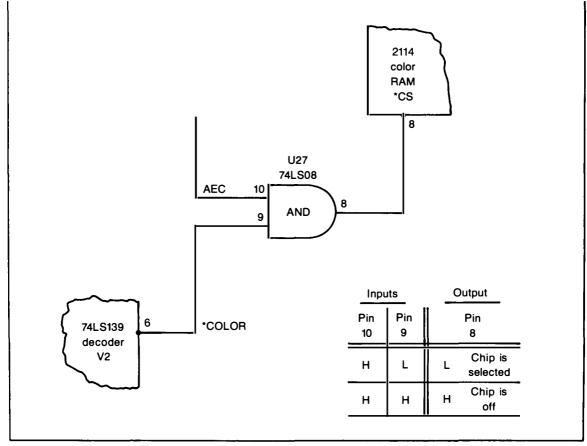

| 8-3       | 74LS08  | Quad 2-Input AND    |

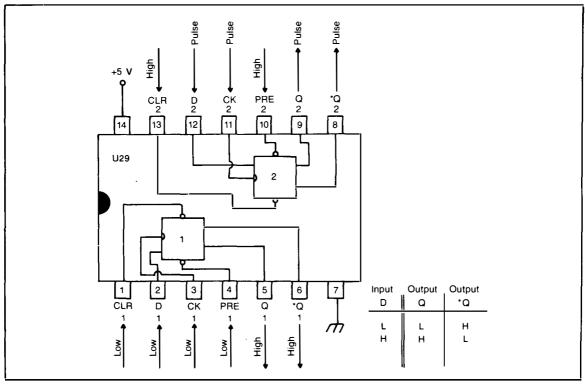

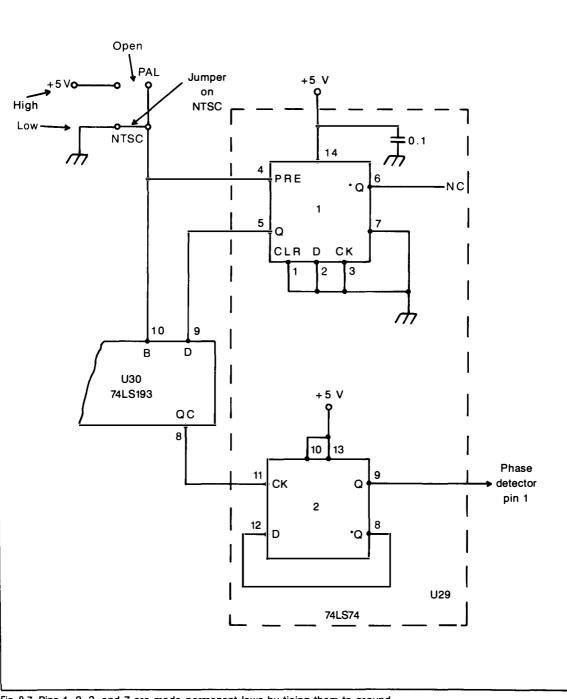

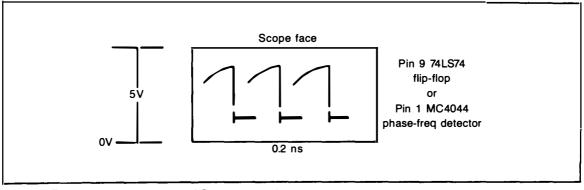

| 8-6       | 74LS74  | Dual D Flip Flop    |

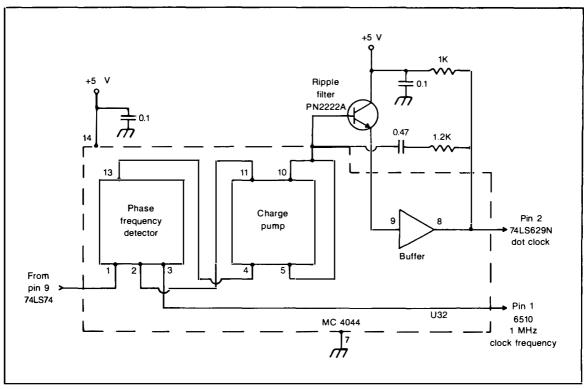

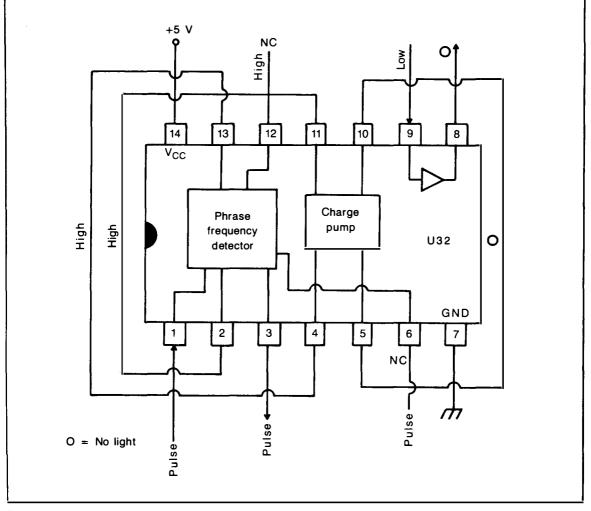

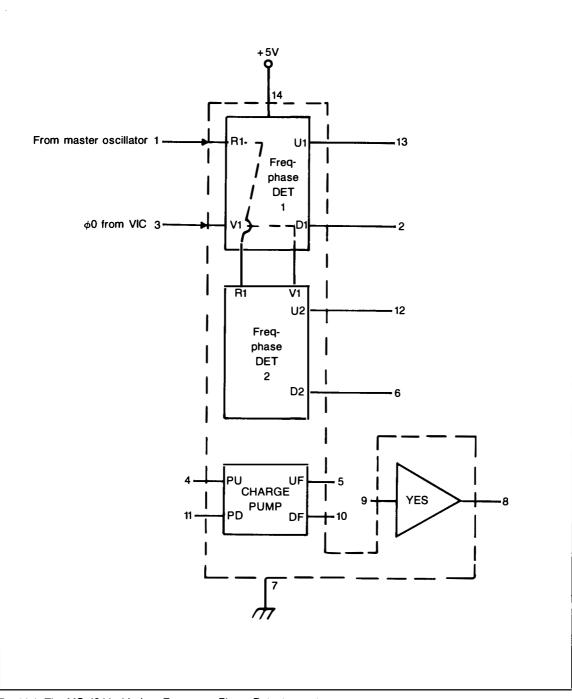

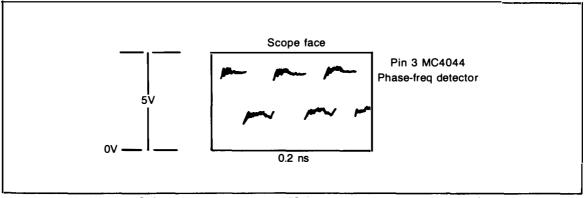

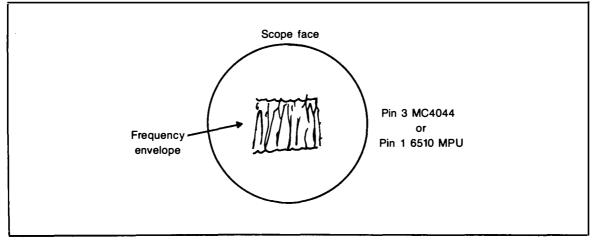

| 8-9       | 4044    | Phase/Freq Detector |

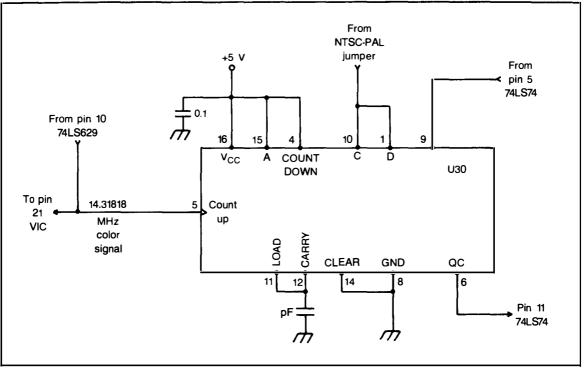

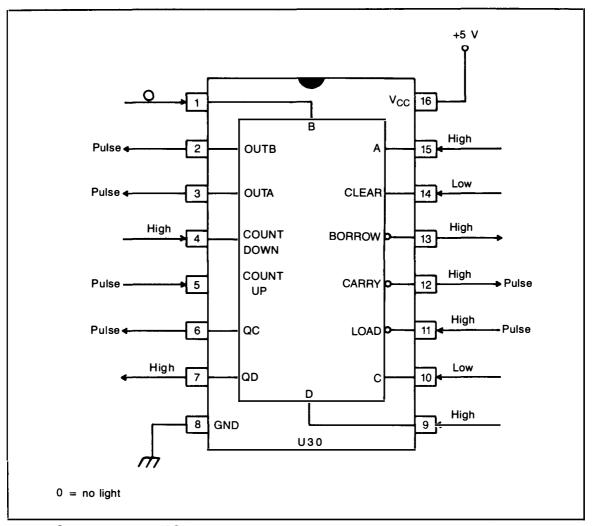

| 8-11      | 74LS193 | Up/Down Counter     |

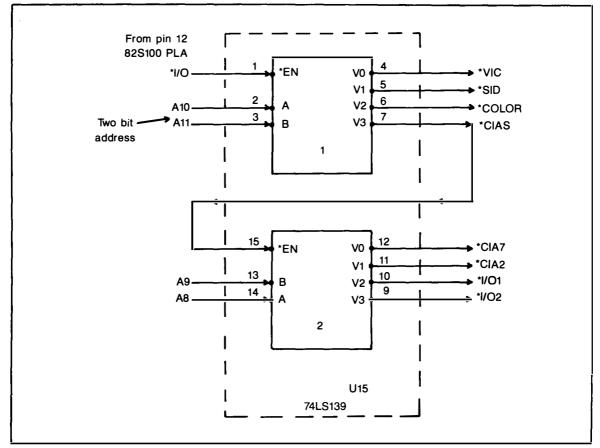

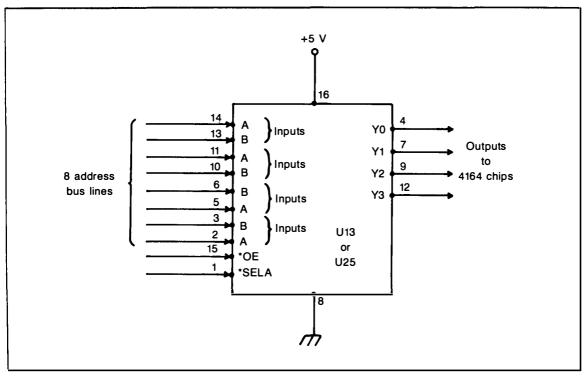

| 8-14      | 74LS139 | Decoder             |

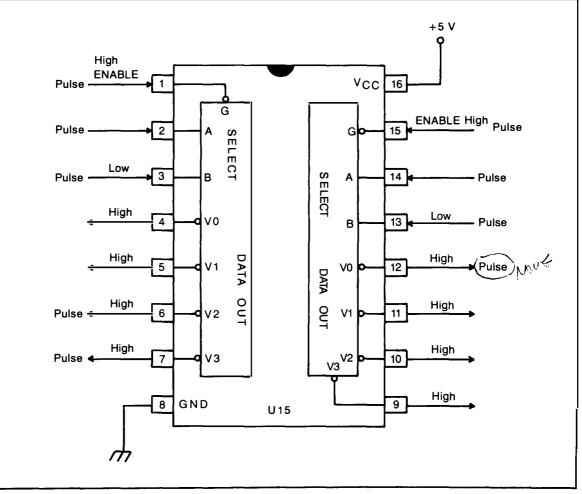

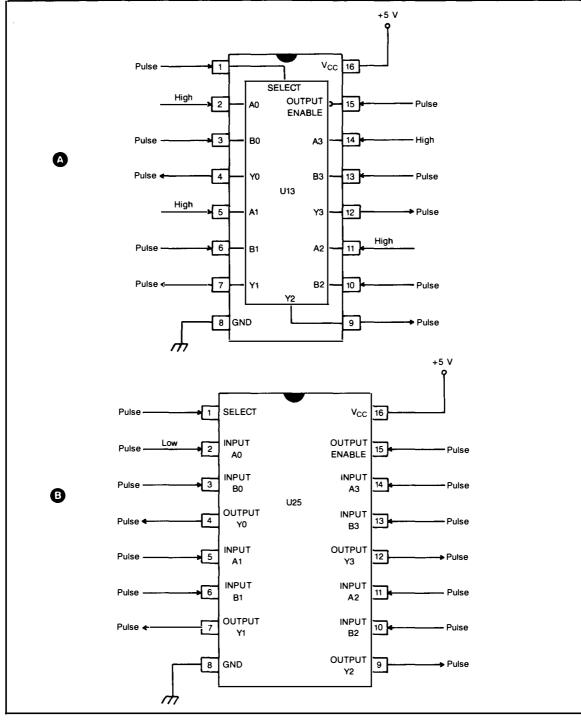

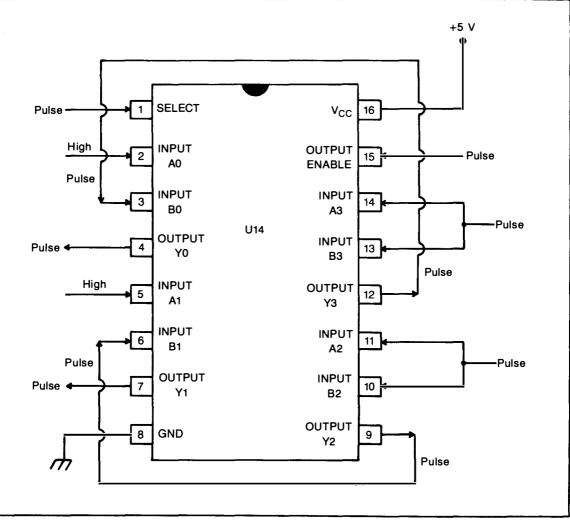

| 8-16a,b,c | 74LS257 | Multiplexers        |

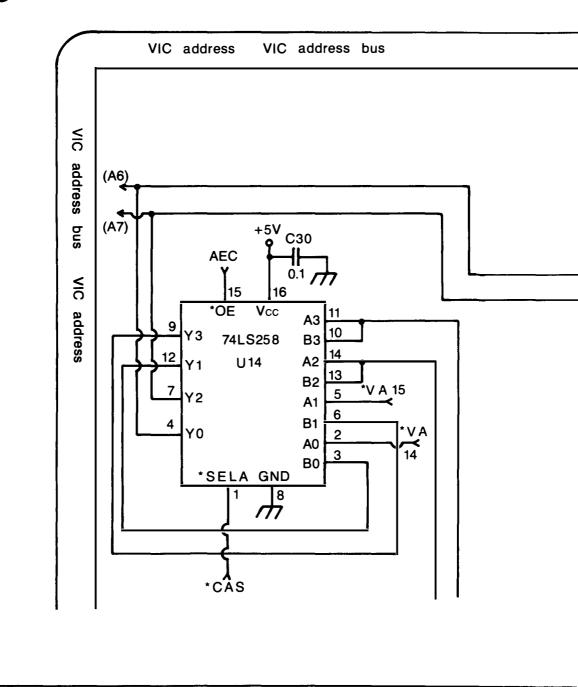

| 8-17      | 74LS258 | Multiplexer         |

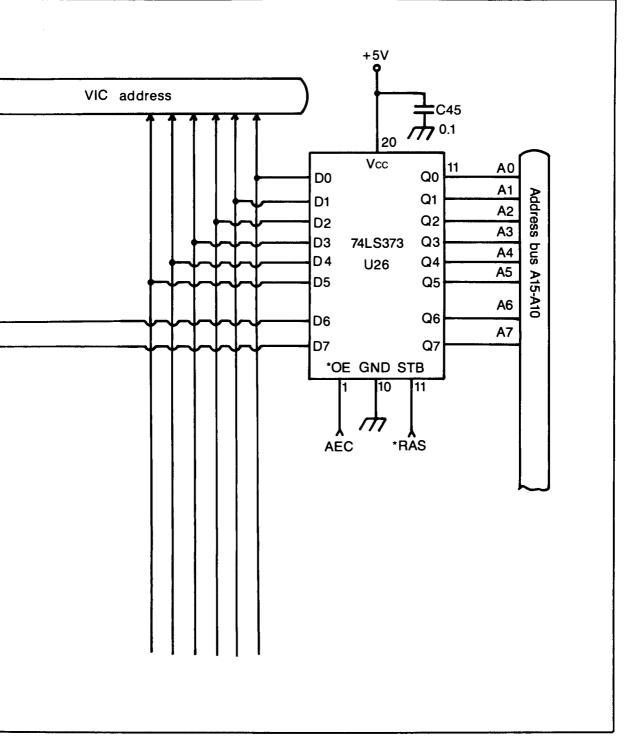

| 8-21      | 74LS373 | Octal Latch         |

| 8-25      | 4066    | Quad Switch         |

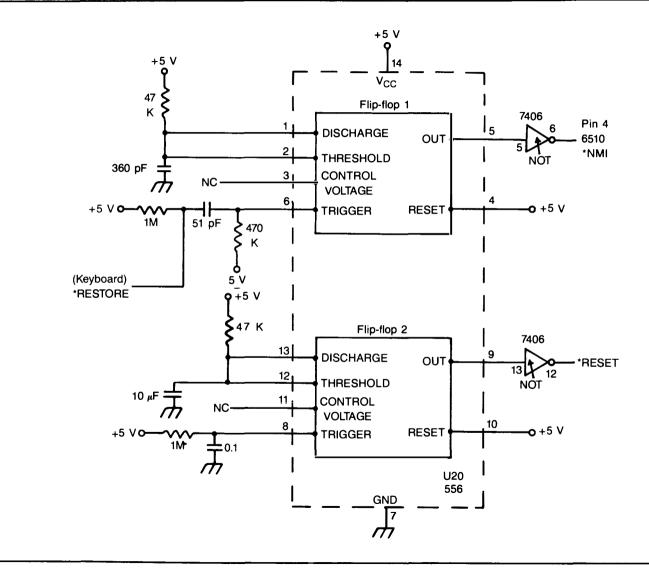

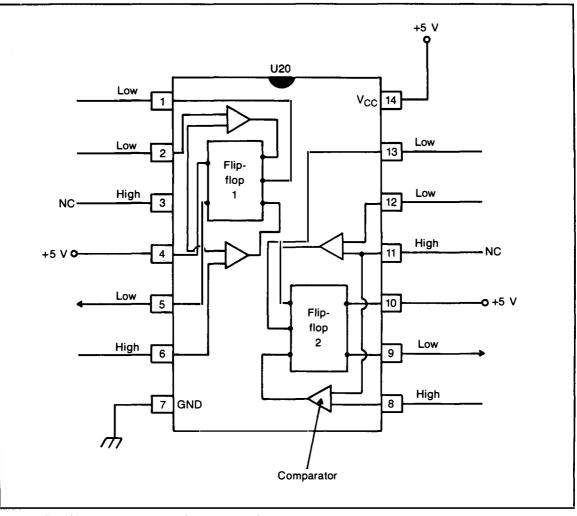

| 8-27      | 556     | Dual Timer          |

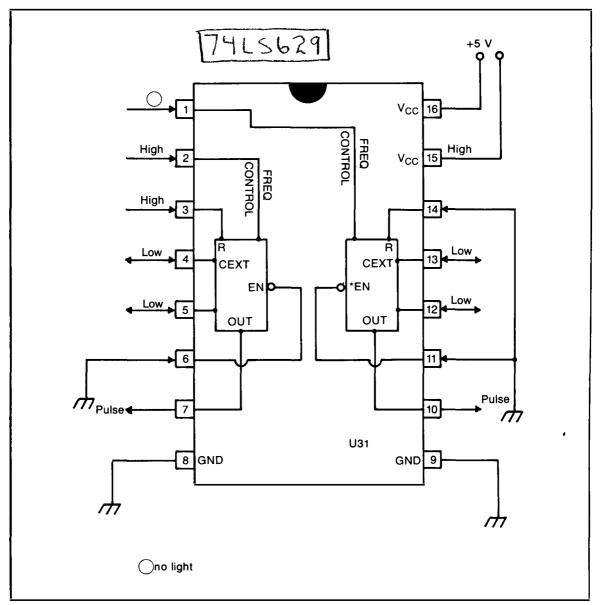

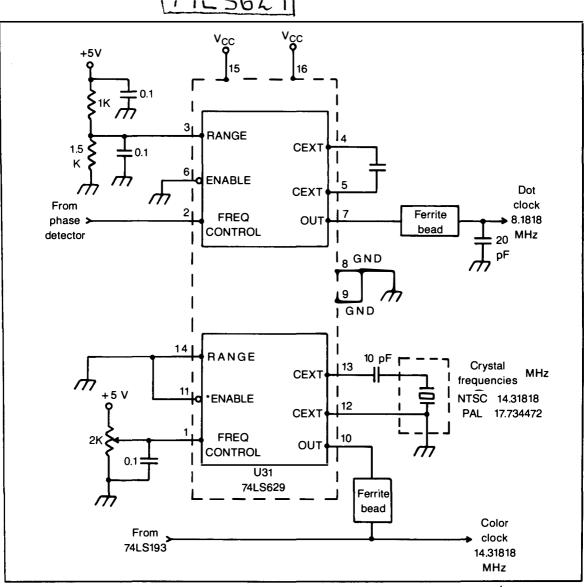

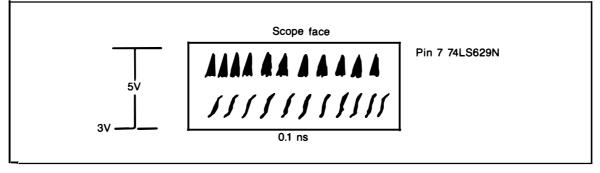

| 8-28      | 74LS629 | Dual Voltage Osc    |

| 12-16     | 6510    | Microprocessor      |

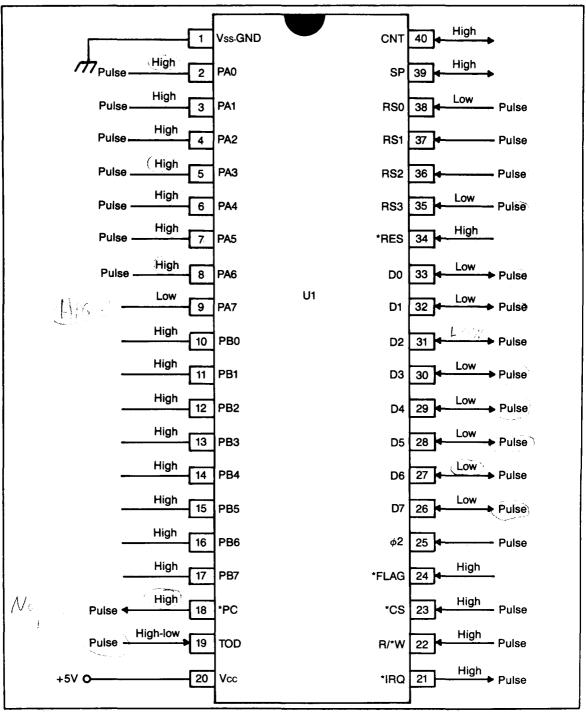

| 16-8      | 6526    | CIA 1               |

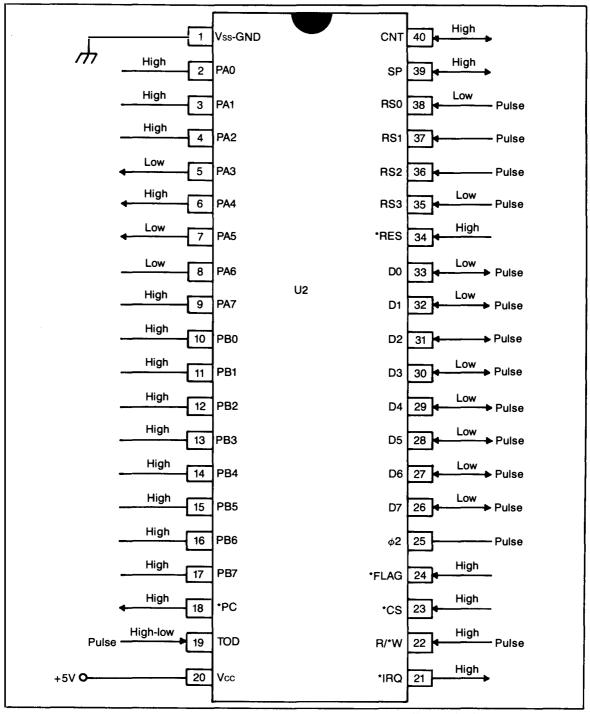

| 16-9      | 6526    | CIA 2               |

| 17-15     | 6567    | VIC II              |

| 18-1      | 6581    | SID                 |

# Introduction

When I first turn on my Commodore 64, there is a pause between the time the switch is flicked and the blue on blue picture comes on with the READY sign and the blinking cursor. It's little more than a second, but the pause makes me nervous. The thought always flashes through my mind: come on, fellow, come on.

Unfortunately, with the millions of 64s in daily use, even though the 64s are quite reliable, they are still only assembled pieces of electronic gear. On any given day there are many of them that do not come on. If yours is one of the unlucky, what can you do? Obviously, the reason why your little favorite is not coming on will have to be discovered.

That is what this book is all about. Even though you might be a top programmer or an expert computer operator, the troubleshooting and repairing of your 64 can only be accomplished by approaching the machine from a different point of view. It will be easier to gain the technician's viewpoint if you are a programmer or operator, but the approach is a new one and requires a different dimension of thought. The analogy has often been given that the programmer can be compared to the driver of a car. Just as the auto driver does not need to know how the car's engine burns gasoline, the programmer does not need to know how the computer's circuits are consuming electricity. When the auto breaks down, the driver takes it to a mechanic for the fix. In the same way, a programmer can take an ailing 64 to a computer tech for the repair. You could think of this book as the manual the tech refers to as he makes the necessary tests to get the machine back into operation.

However, this book is much more than that. Besides the needed specific information on voltages and parts, this is also a training course to give Commodore 64 owners the information that, added to programming skills, will give you the missing dimension that will enable you to gain mastery over your computer.

In order to be able to figure out and repair a circuit failure in your 64, you must first of all be able to picture in your mind how the circuit is working. There are also tried and true electronic service

pathways that have been developed over the years. By following these methods and using your puzzle solving abilities, you will be able to locate defective components or connections. Once the trouble is pinpointed, which is the most trying part of a repair job, then the rest of the chore is either replacing the part or repairing the connection.

The starting point of any repair is to carefully analyze the symptoms of trouble. The computer not coming on is only one symptom. There are a number of others. In Chapter 1, all the common symptoms are discussed. Each symptom points to a circuit area that could possibly contain the source of the trouble. In each circuit, there are primary suspects that should be examined first. However, in order to get to the circuits you must be able to take the 64 apart. It is not difficult, and Chapter 2 shows you how. It's all up to knowing where the screws are. Dismantling the machine must be performed correctly and carefully to avoid accidents. A wrong move could cause additional troubles that can really complicate things.

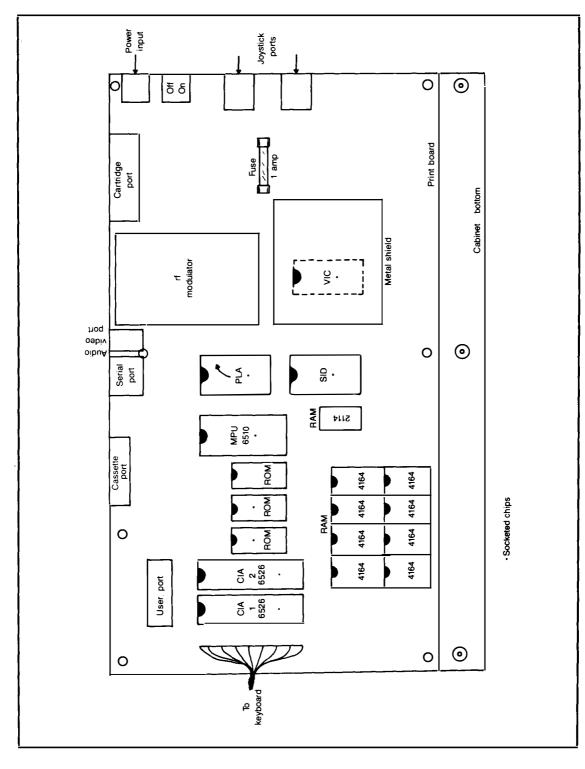

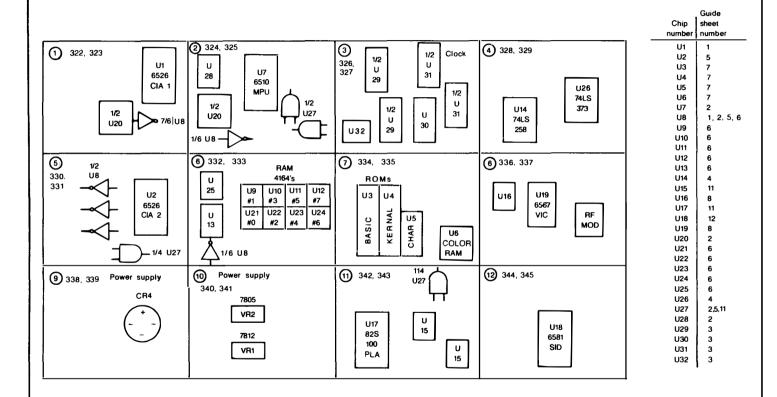

Chapter 3 contains the most used piece of service information—the Chip Location Guide. This is the Printboard layout of the 32 chips in the computer. It lets you relate all the information you learn to the location of any chip you might want to examine on the board. This Guide will be used on every repair job and will be constantly referred to during the course of the troubleshooting. It is indeed valuable.

Chapter 4 is the directive that provides the mechanical and electronic techniques that must be used if and when chips have to be replaced. The tools and thinking that goes into the ticklish job of changing an IC is reviewed. Changing a chip is not at all like changing a vacuum tube and similar but much more exacting than changing a transistor. These first four chapters, amazingly, will teach you how to repair quickly at least 50 percent, and possibly more, of possible breakdowns.

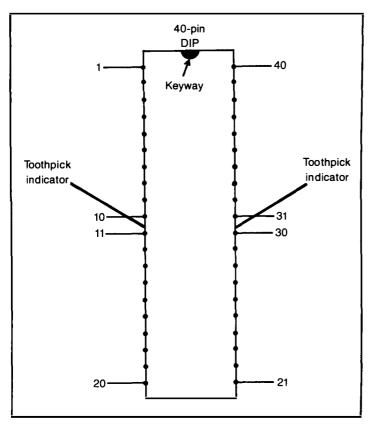

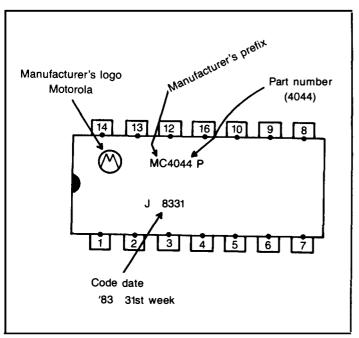

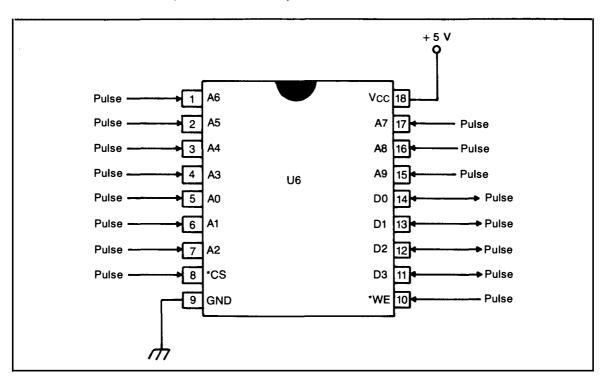

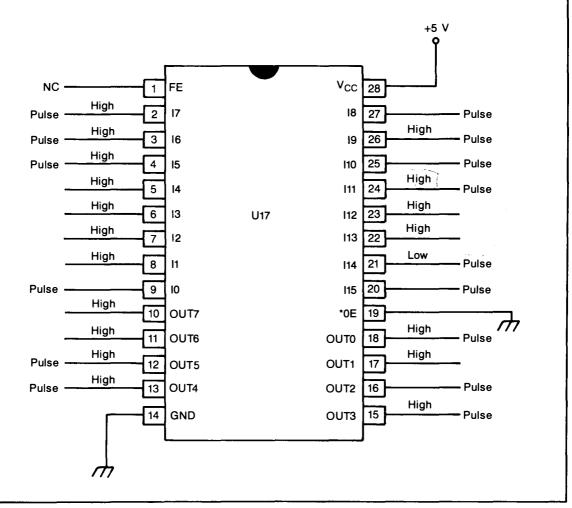

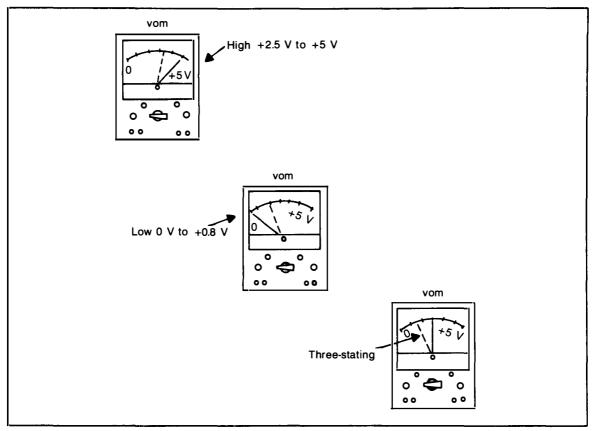

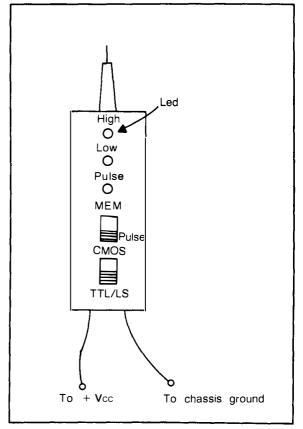

Chapters 5 through 8 introduce you with a bit more intimacy to the chips in your machine. Starting in Chapter 6 you'll find the first of the 21 Test Point charts that make it easy to quickly check out every chip in the computer. Each chart is the top view of a chip showing the exact pinout. The name of each pin is given and, where practical, a sketch of the chip's insides. Then arrows point the direction of the signal flow. Attached to each arrow is the actual reading you should receive if you probe the test point with a logic probe or vom.

The readings were all made on my Commodore 64 with my logic probe and vom. The readings were taken when the computer was first turned on with the READY sign on and the cursor blinking. The idea is when you read your chips the state of each test point should match up with my charts. If the chip reads correctly, then that chip is deemed ok. Should one or more readings on a chip be incorrect, that is a symptom of trouble and bears further investigation.

Actually, what you are doing is checking the input and output status of the chips. The inputs and outputs are clearly shown by the arrows. If all signals are being input properly but not outputting correctly, chances are the chip's internal circuits are not passing the signals. That would indicate a bad chip. Should an input signal be incorrect, odds are the chip is ok but the circuit feeding the chip is not getting the signal to the pin. That circuit or bus line could have a short or an open condition. The 21 charts are your entree to getting repairs underway quickly and locating troubles fast.

You'll find the charts in Chapters 6, 7, 8, 12, 16, 17 and 18. A list of the Test Point charts is found immediately after the Table of Contents.

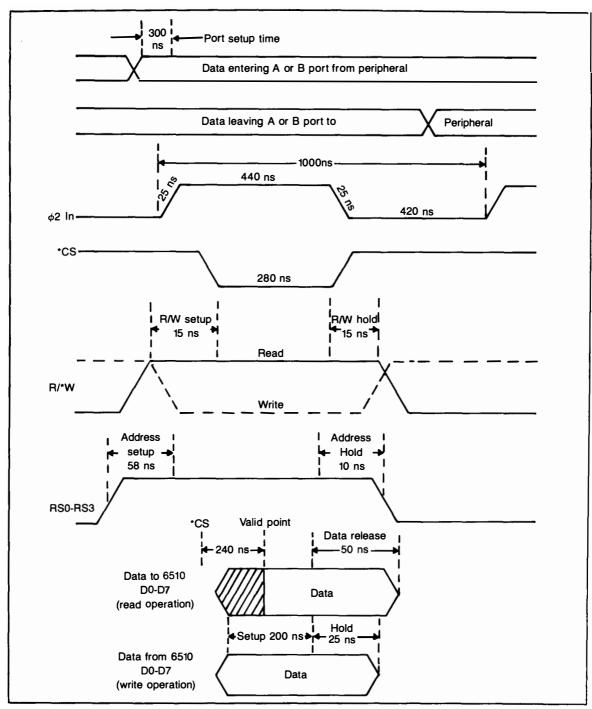

Chapters 5 through 20, besides being a servicing manual, are also, with the exception of Chapters 10 and 11, a technical reference manual written on a technician's level. There are discussions of each chip with considerable detail and even some timing diagrams for the 6510 MPU, RAM and the CIAs. You can really gain mastery over your machine by gradually absorbing the material. You'll find your programming skills will improve immeasurably as you gradually realize what is actually happening to the 1's and 0's as they flash around the digital circuits.

The book ends up with a Master Schematic of your machine. The schematic is needed during a difficult repair after the circuit area containing the trouble has been located and the wiring details are needed to pinpoint the prime suspects. The schematic contains all the part numbers. These same part numbers are found printed clearly on the print board. For example, a U7 is found printed on the board next to the 6510 MPU. The schematic reads U7 as the part number for the MPU. All the capacitors, resistors, etc. are identified in the same way. With the Chip Location Guide, the Test Point charts, the theoretical discussions of the circuits, and the Master Schematic, you should be able to cover all the information needs you'll ever require for troubleshooting and repair of your computer.

Chapters 10 and 11 act as a short course in logic gates and digital registers with specific reference to the gates and registers in your computer. The machine's numbering methods are included too. The BASIC language in your 64 uses ordinary decimal as its number system. The 64 changes the decimal to binary and then after processing changes the binary back to decimal once again. With the PEEK and POKE commands, you can signal trace circuits that the MPU is able to address. The ability to convert from decimal to binary and then back should be one of the tools in your servicing repertoire.

From a money and convenience point of view, it really pays off to be able to at least make the easy repairs on your computer. The easy ones are at least half of the total. While your 64 is still in warranty, there is no problem. Should your machine give up the ghost during the first 90 days, all you have to do is take it back to the dealer. He will give you a new one. Commodore is very accommodating that way. However, once the warranty period is over, the complication begins. If the machine fails, you must send it back to the factory repair facility. This usually takes some weeks and it is returned with a healthy repair bill. If you are able to do the troubleshooting and repair yourself, the savings in time and money is quite worthwhile. If you happen to get one repair in the life of your machine from this book, it will more than pay for the price of the book.

I'd like to thank my wife Lea for running interference and fielding interruptions while I wrote the book. I would also like to thank my son-in-law Michael Gorzeck for taking the black and white photos. I hope your computing is uninterrupted, but should your 64 act up, perhaps this book will be directly responsible for getting it back on line again.

# **1. Interpreting the Symptoms**

**I** N THE OLD DAYS OF COMPUTERS, WAY BACK as far as 1976, before micros hit the homes, users for the most part inputted and outputted through a teletype machine. A teletype cost about \$1000 and was touted as being able to provide almost every function of a computer system. These were considered the keyboard input, the printer output, and paper tape punching and reading. Notice that a TV display is not even mentioned.

There were, of course, TV displays around called CRTs. They were able to show numbers and letters easily. They could produce dot matrix patterns in good fashion. However, graphic pictures could only be produced with equipment that carried astronomical price tags. The CRTs were a peripheral accessory that was not used as much as the teletype. Things have changed.

The TV display is the most used output device for the computer. Teletype machines are almost unknown to the home computer or small business user. Alphanumeric characters, dot patterns, and complicated graphics are routine uses for the computer owner. The TV display is thought of as part of the computer. You wouldn't think of using your Commodore 64 without the TV display.

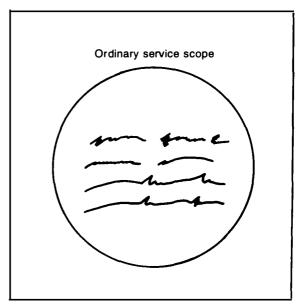

From a troubleshooting and repair point of view, the TV display is a diagnostic tool. When the computer is okay, the TV picture shines in bright colors and the audio emanates correct sounds. If trouble strikes the computer, symptoms of the condition often appear dramatically on the TV screen or are heard from the TV speaker. By careful eyeball analysis, the troubleshooter is often able to pinpoint the seat of the trouble, or at least know where to start.

#### **COMMON SYMPTOMS**

The following collection of general symptoms can help you determine which section of your computer has failed. Narrowing down the location of the problem is the first step in troubleshooting. Let's give these troubles some thought.

#### **Dead Computer**

The most common problem that you'll en-

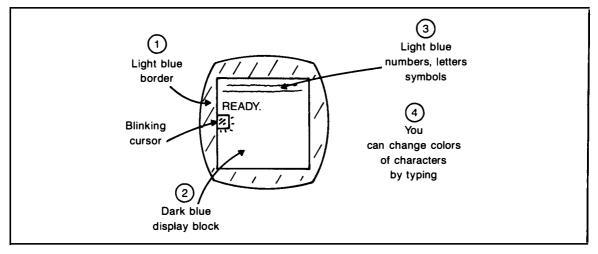

Fig. 1-1. When your TV brightness comes on ok but your 64 won't display anything, your computer is playing dead.

counter is a blank TV screen. You have your 64 connected to the TV ok, and the TV is showing light probably with snow (see Fig. 1-1). When you

flip the off-on switch, nothing happens. The LED pilot light could shine red or not show light at all.

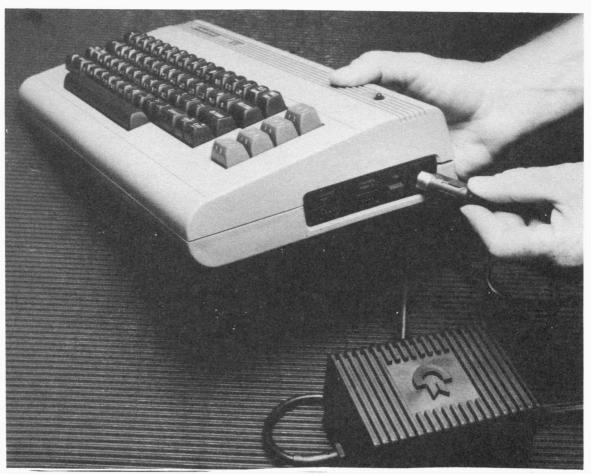

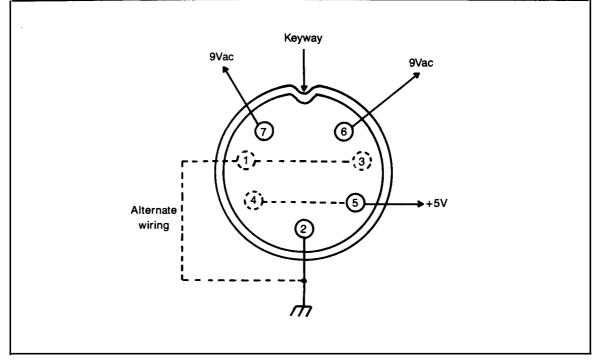

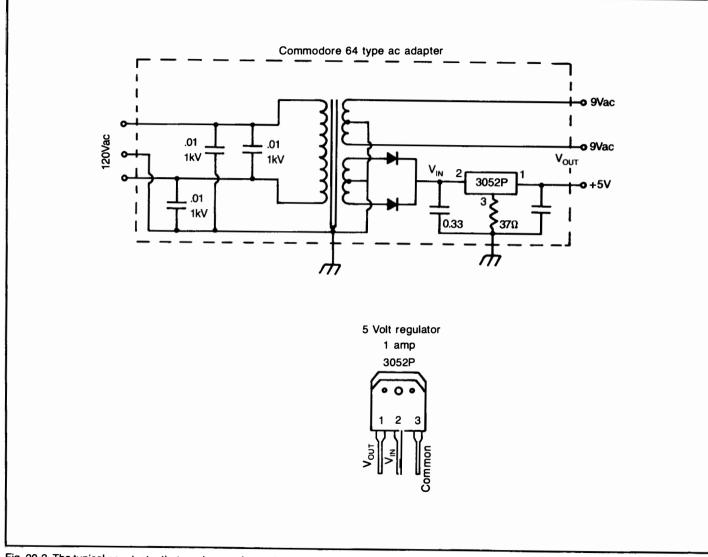

Of course, you must be sure that the computer is plugged in properly at both the wall socket and that the power cable shown in Fig. 1-2 is plugged into the side of the case. If everything is plugged in, feel the casing of the ac adapter for your 64. Is it getting warmish? If it is, then it is probably ok. If it is not, it could be the trouble. Trying a new one will prove the point. If a new one works then it was bad. Should the new not work either, then the old one is probably fine.

Once you complete the above quick checks and the computer is still dead, then turn to Chapter 20

Fig. 1-2. The first obvious step to take when your 64 acts dead is to make sure it is plugged in at the wall socket and at the side of the case.

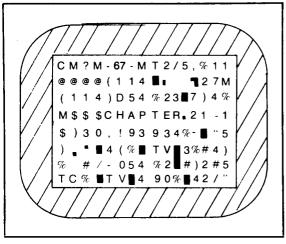

Fig. 1-3. When the TV fills with GARBAGE instead of the READY sign and the blinking cursor, there is some trouble in the digital circuits of the computer.

for the next troubleshooting steps. You'll need to take the 64 apart and make some ac and dc voltage reading with a vom.

#### **Garbage Display**

The next most common symptom is called "garbage."The extreme case of garbage is shown on the screen in Fig. 1-3. When you turn on your 64, the TV display immediately fills up with

numbers, letters, symbols, white spaces and black spaces. It looks like a cartoon character's collection of swear words. Your 64 should have come on with the READY sign, but you are looking at garbage instead.

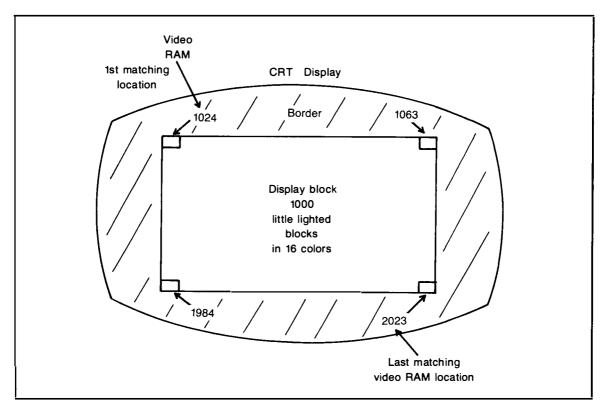

The TV display is normally able to show the four items (Fig. 1-4). The border should come on in light blue. Second, a dark blue display block should appear contained in the border. The third item in the picture consists of numbers, letters, and symbols. The lettering ends in the word READY. The characters that the 64 displays upon turn on are also in light blue. The display is also capable of changing the color of the characters. The colors do not appear automatically upon turn-on. You must type in the colors you want.

The reason why garbage appears on the screen, instead of the two-tone blue, sign-on message, is because the microprocessor is running wild. Normally, the processor performs its duties under the careful control of the 64's operating system, which is contained in the ROM chips. When the operating system for some reason loses control, the processor simply goes mad, spewing addresses, data and control signals without any rhyme or reason. The result is, the TV display fills up with meaningless characters, numbers, symbols, and spaces.

The garbage can be caused by failure in almost

Fig. 1-

and the ability to have the character colors changed easily.

any of the digital circuit components or chips. The approach to first locating the general circuit area of the trouble and then pinpointing the actual failed component or connection requires the following. You must learn how the digital circuits are processing data from a hardware point of view at a technician level of understanding. Then you can intelligently make voltage, logic probe, and scope readings to seek out defects. Chapters 5 through 16 contain the information that will help you discover what is causing a garbage condition.

#### **Empty Display Block**

A related trouble to garbage happens when the border and display block come on ok, but none of characters are appearing. You can strike the keyboard to your heart's content, but nothing happens. The block remains empty. Refer to Fig. 1-5.

Here again the same circuits are suspect. The condition could possibly be located anywhere in the digital circuits. It is the troubleshooter's job to take test readings and from the results of the readings deduce what circuit area is in trouble. Understanding Chapter 5 through Chapter 16 should clear up the maze of chips and print board copper traces.

These chapters contain troubleshooting techniques and schematic drawings with the voltage readings and logic states that are normally present on the test nodes when the READY sign appears. If you run some tests and one or more of the test results do not match up with what is supposed to be at the connections, you have found a clue that could lead to the fault.

#### **No Color**

The 64 is a color computer. It has circuits that produce colors that are placed into the TV display. When the computer is putting out a correct display of characters and symbols but will not show any colors, it indicates that the trouble is in the color circuits.

The color signal originates in the clock circuit. Chapter 14 covers the system clock. The color is output by the Video Interface Chip, or VIC. Chapter 17 reveals the VIC workings and its associated cir-

Fig. 1-5. A variation of garbage is an empty display block. The border and display block appear but no characters appear. Striking the keyboard has no apparent effect.

cuits that could be involved in the "no color" symptom.

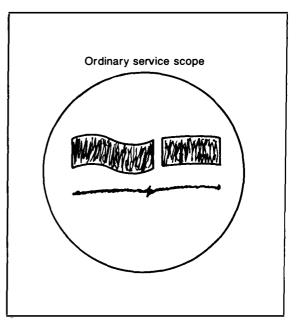

#### No Video, Sound Ok

This symptom resembles the "dead set" power supply troubles except for one thing, the sound is ok. This means the digital circuits are working. The trouble in this case is in the video output circuits. The VIC and its output transistors are the probable cause of this malfunction. They are covered in Chapter 17.

#### No Sound

When everything is working except the audio, the trouble is located in the area of the sound circuits. Chapter 18 covers the 64's sound circuit inside and around the Sound Interface Device, or SID.

#### **External Device Troubles**

The 64 is able to receive inputs from the keyboard, the joysticks, the paddles, a cassette, the disk system, and many other devices. It is able to output to a printer, the cassette, the disk drive, and other external units. When these units start acting up the trouble could be either in the device itself

or the I/O circuitry that connects the device to the computer.

If you have device problems, the first step is to try another known good device. If the new device works, then the old one was defective. Should the symptoms remain with the new unit, then the problem is being caused by the computer. Chapter 19 covers all the interface connections on the back and side of the 64 that devices can plug into. Chapter 16 covers the I/O chips that the plugs connect to inside the 64. This type of trouble is usually confined to these circuits.

The keyboard is connected internally to the I/O chips in the 64. Figure 1-6 shows the keyboard wires disappearing into the 64's innards. When the keyboard does not work properly, you can test it as if it is part of the computer and not an external device. The keyboard connections are discussed in Chapter 16.

#### **DIAGNOSTIC PROGRAMMING**

Odds are you have already spent a lot of time work-

Fig. 1-6. The keyboard is connected inside the case at a special plug on the print board. The keyboard is disconnected only as a troubleshooting or repair measure.

ing on BASIC programs on the 64. BASIC programming can be a very important tool to isolate circuit sections where troubles might lie. I use BA-SIC programming as a signal injection technique. The function PEEK and the statement POKE are the mechanisms that perform the signal injections. They are powerful troubleshooting test instruments. You can write your own diagnostic programs or buy commercial software to perform tests.

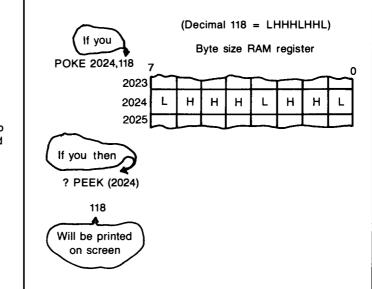

#### **PEEK and POKE**

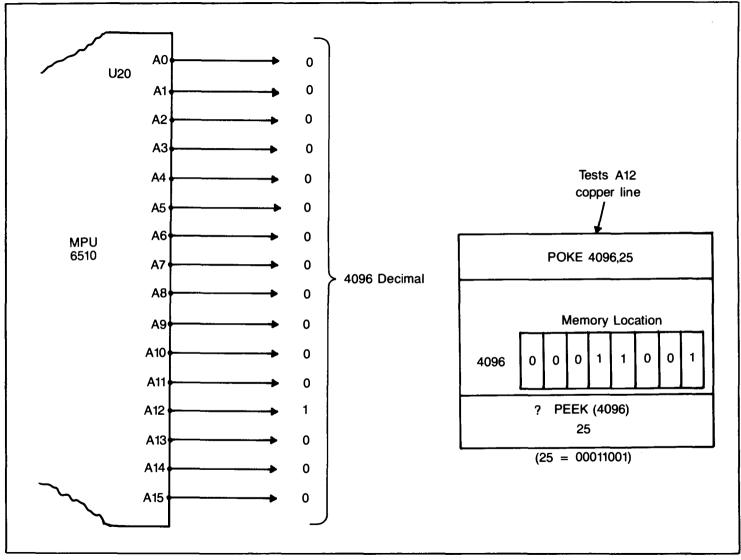

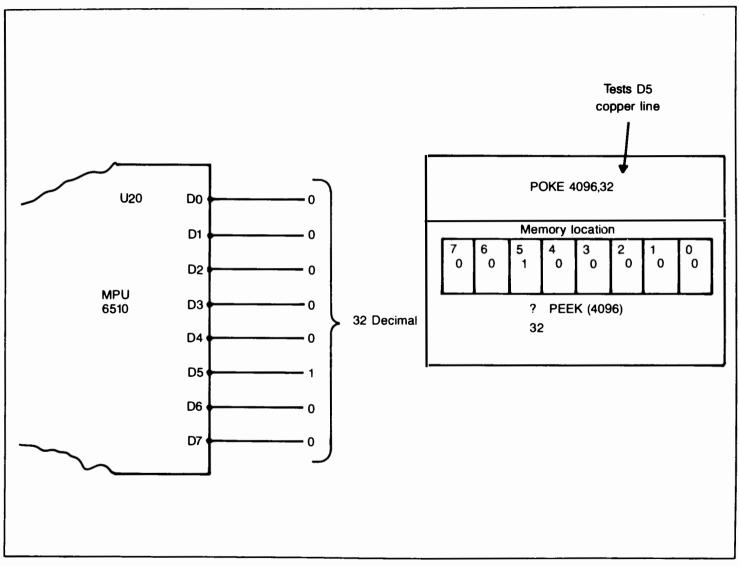

Peek allows you to read the contents of any of the thousands of locations in the 64's memory map. POKE permits you to load a byte of data into all of the memory map addresses except the read-only locations. This gives you tests whereby you can run data back and forth from the microprocessor to all locations of the memory map.

The PEEK and POKE tests work in the immediate mode or contained in a program. It should be obvious, however, that diagnostic software tests have their limitations. If the computer is dead or the processor is out, you cannot use the test functions or statements. They simply won't work. On the other hand, when the computer comes on normally and displays READY and the blinking cursor, you can try the software testing. Chances are good it will provide you with some valuable service

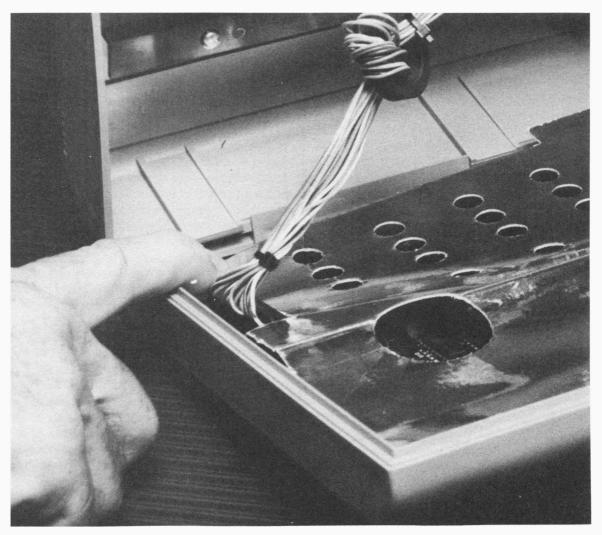

Fig. 1-7. When the technician sees the PEEK return decimal number 184, he knows that location 209 contains the voltages HLHHHLLL.

information to guide you to the ultimate repair.

The PEEK and POKE used for troubleshooting requires that you have a clear idea of the relationship between decimal numbers and the set of bits they represent. When you PEEK a memory location, a decimal number is returned to you and is printed on the screen. The decimal number is the code for the set of eight bits contained in the register you have just read.

For instance, suppose you tell the 64 to PRINT PEEK (209). The 64 returns the decimal number 184. The 184 is the decimal code for the binary bit collection 10111000. Figure 10-7 illustrates this idea. The bits could also be described as HLHHHLLL. The programmer usually thinks of the bits in terms of 1s and 0s while the technician finds the Hs and Ls more convenient. Anyway, the PEEK function has permitted you to read the contents of location 209. In certain cases, learning the bit contents is a piece of valuable service information.

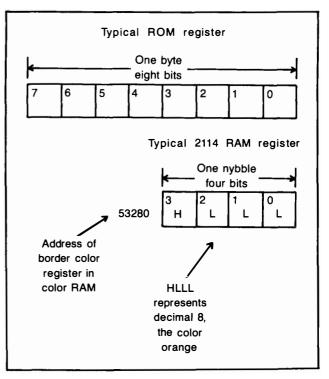

At other times in a repair process, it might become necessary to write a set of bits to a location. For example, if you want to quick check the color RAM chip, you could write to the location that changes the color of the border. If you enter POKE 53280,8 the border of the TV display should change to orange. Try it. If it does, then the color RAM chip seems to be working ok. When the POKE produces no effect or the wrong effect, the chip could be in trouble. At any rate, the 53280 is the decimal address of the color RAM register. The 8 is a set of bits, 00001000 or LLLLHLLL. The color RAM uses the four lowest bits, HLLL, to change the border color.

PEEK and POKE can be used throughout the entire memory map, which contains 64K of dynamic RAM and additional memory locations for static RAM, ROM, and I/O. The servicer must view the locations as bit holders and the decimal numbers as code for the bits. There will be a lot more detail on this subject in Chapter 10 and Chapter 11.

#### **Diagnostic Programs**

Besides being able to read or write to individual addresses with PEEK or POKE in the immediate

mode, you can write programs that perform a whole battery of tests and check out large portions of the memory map. One way is to place PEEK and POKE statements in loops. A POKE statement in a loop can make the 64 write to a large group of memory locations. A PEEK function in a loop could have the 64 read many memory locations and print the results in decimal on the screen. Another way that PEEK and POKE can be used is to test memory locations and the bus lines to the locations. You could first POKE some data to a location. Then you would PEEK the location to see if the data ever arrived. This could all be contained in one program. There are examples of this technique in Chapter 13 and Chapter 15.

In addition to writing your own diagnostic programs as you need them, there is software available that will perform some limited jobs. One piece I've seen in the software stores is a program called 64 DOCTOR. It is manufactured by Computer Software Associates, 50 Teed Dr., Randolph, MA 02368.

It is useful and will normally operate when the 64 comes on ok. The program comes on a disk and also on cassette tape. I only saw the disk version.

It takes a few minutes for the disk to load the program into the 64. Then a menu gives a number of options. There is one test that checks out the disk system and the 64's internal RAM. Next there are tests for the keyboard, a printer (if it is attached), a cassette (if it is attached), and joysticks. Another test provides patterns for the color TV or monitor. The tests are similar to the ones you would use to set up the colors and convergence of any color TV. The DOCTOR also gives the SID chip a music lesson.

The program is interesting and uses the 64's graphic capabilities to full advantage. You'll see sprites that look like a TV, printer, etc. running about the screen as well as all sorts of other patterns. The program was selling for about \$30 at the two places I visited.

While these large diagnostic programs can be interesting and occasionally useful during troubleshooting, they can be especially important before programming. If you are going to be spending days on end programming a heavy project, it is a good idea to exercise the 64, everyday before work. If the machine exercises ok then it is safe to program on. It is very frustrating to spend many hours on a large number of program lines and then find them trapped in the machine.

#### **INSIDE THE 64**

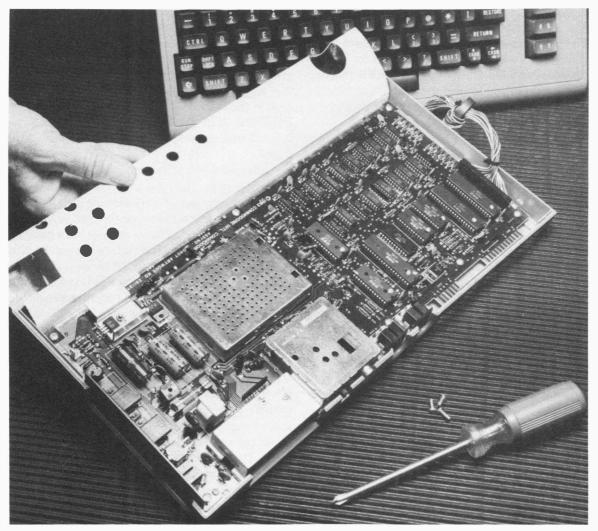

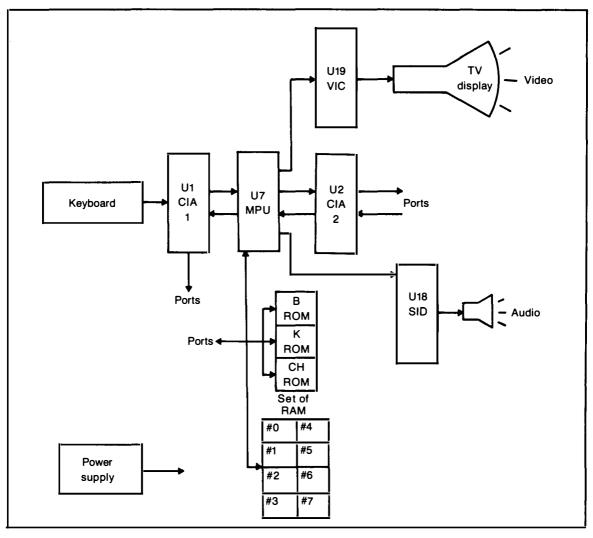

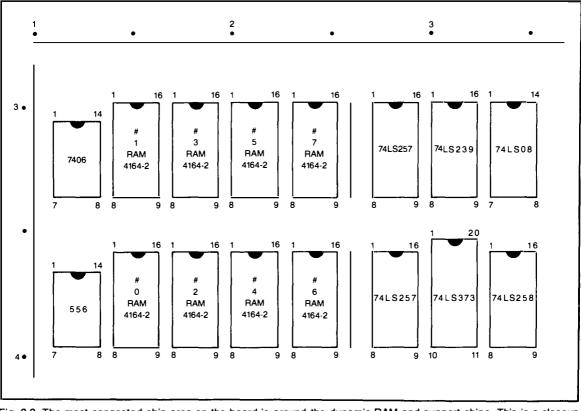

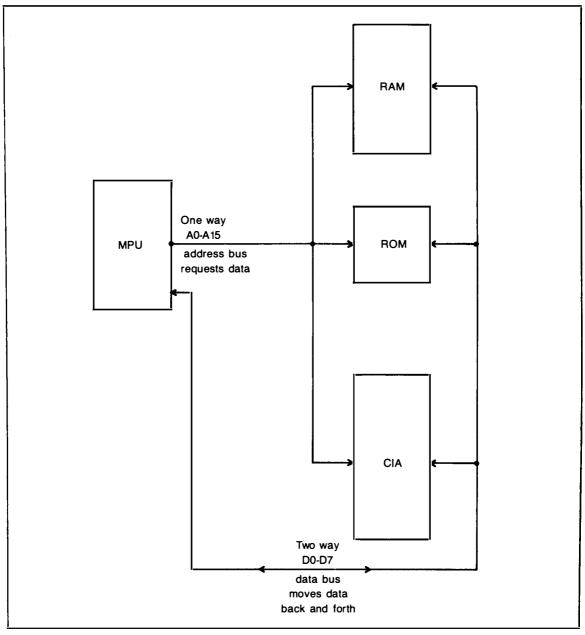

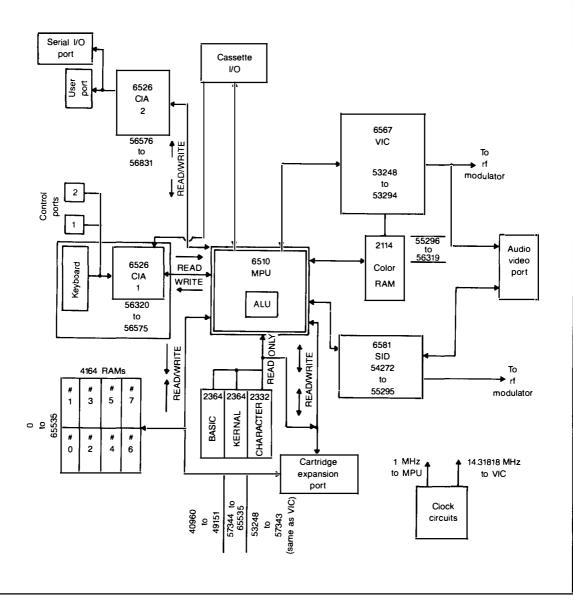

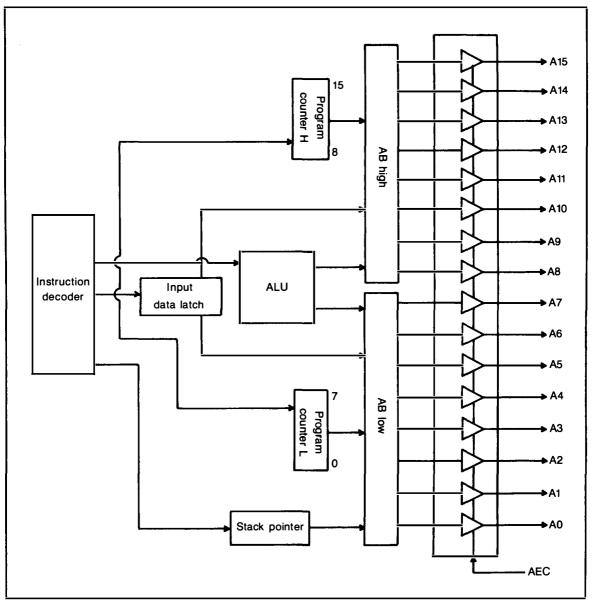

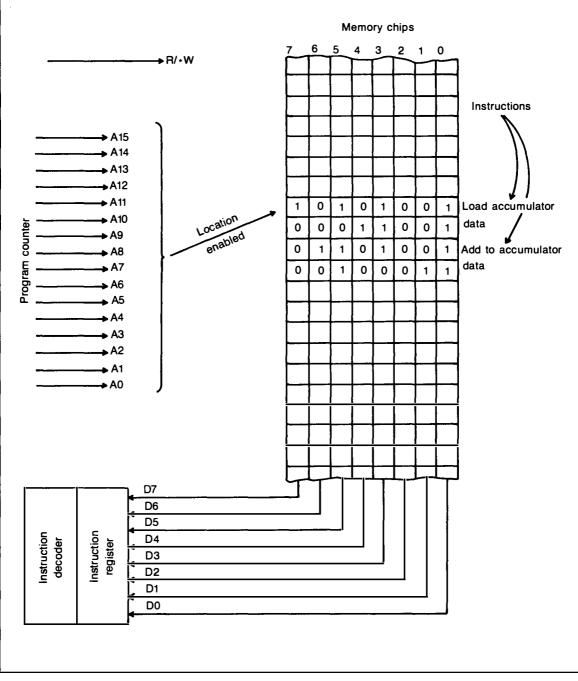

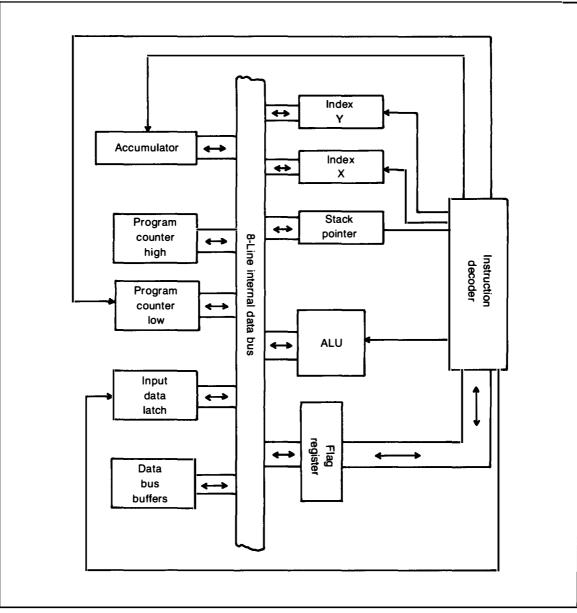

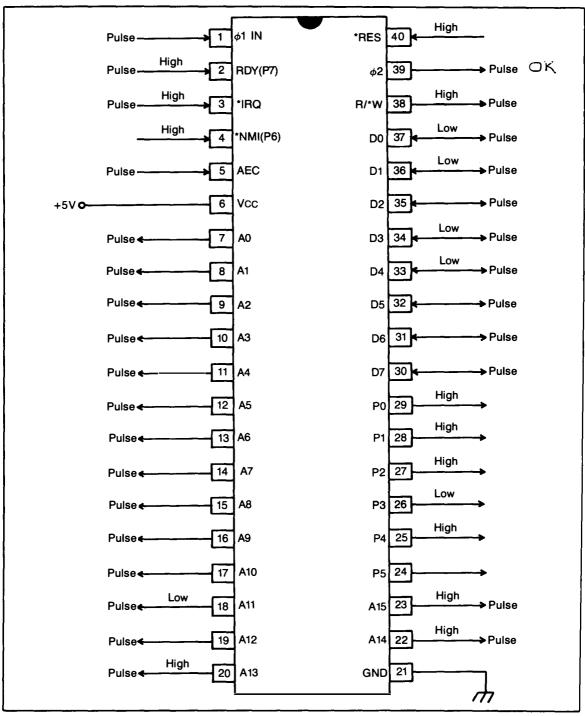

As you look over the 64 circuit board in Fig. 1-8, the main landmarks are the large chips. A closer look shows the data and address buses coursing over the board. Figure 1-9 shows in a very basic manner how these various chips interact.

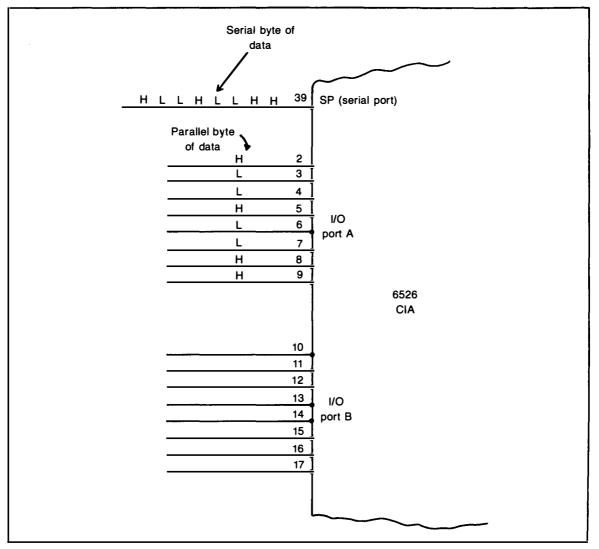

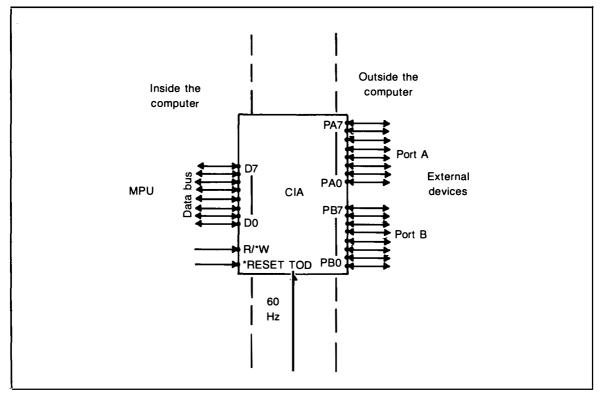

#### **Complex Interface Adapter**

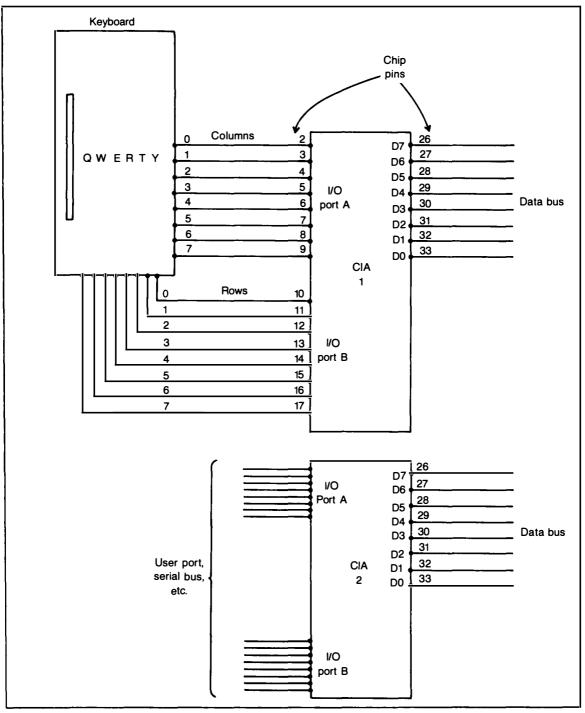

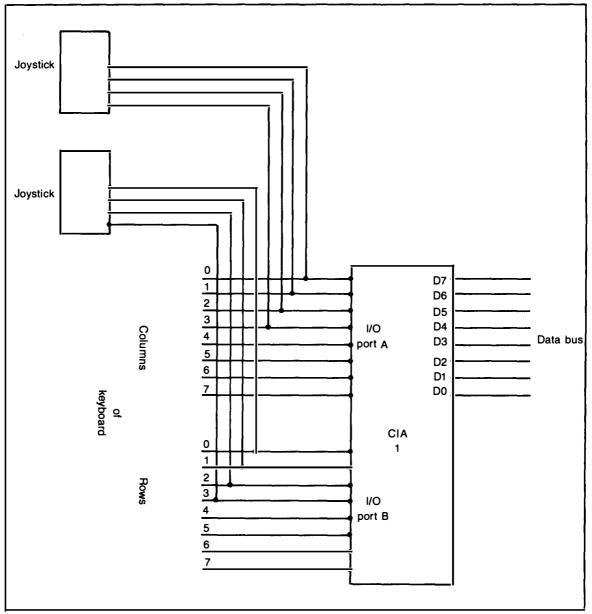

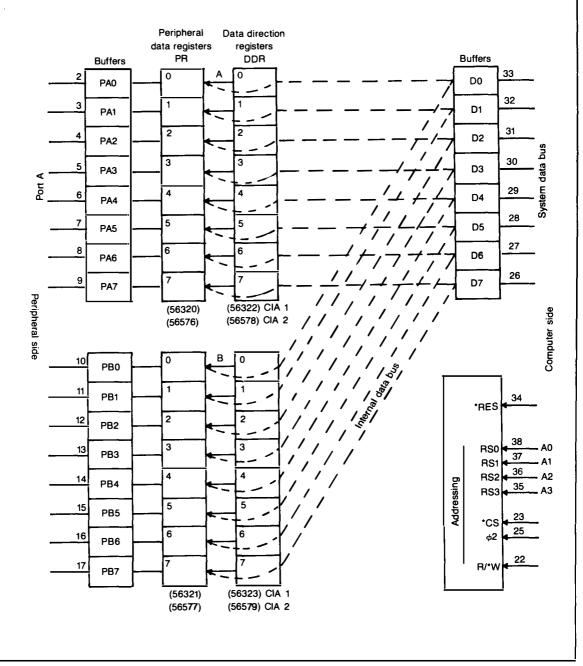

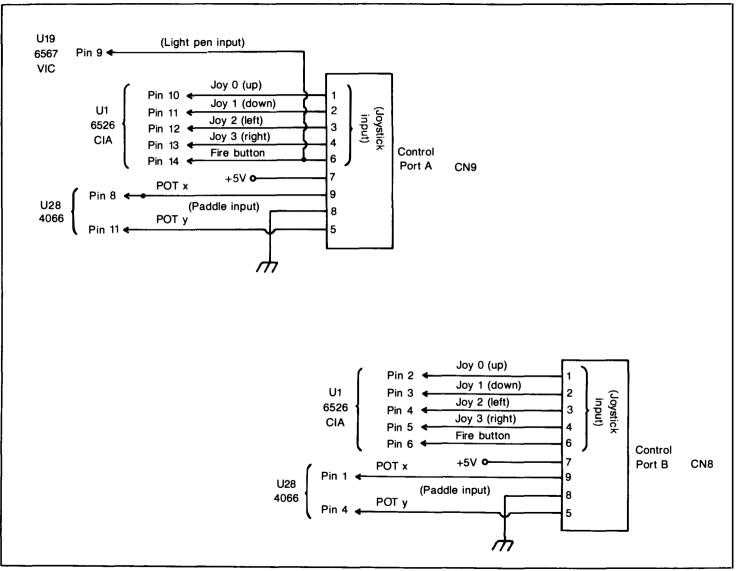

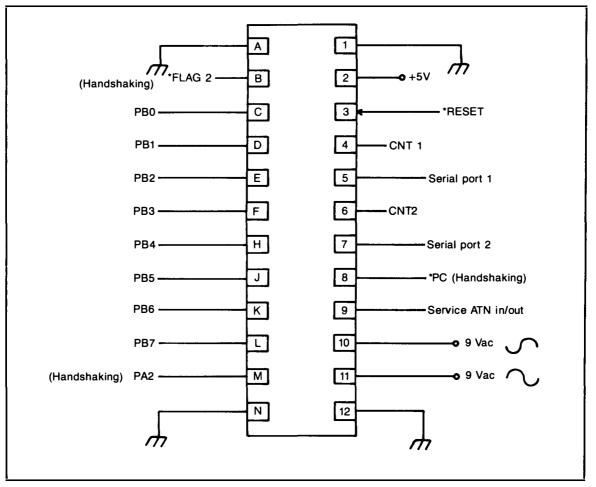

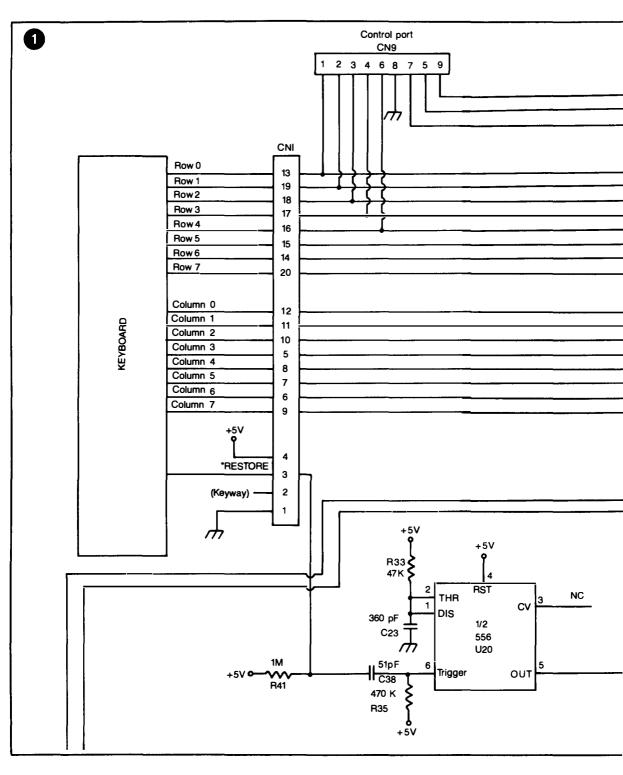

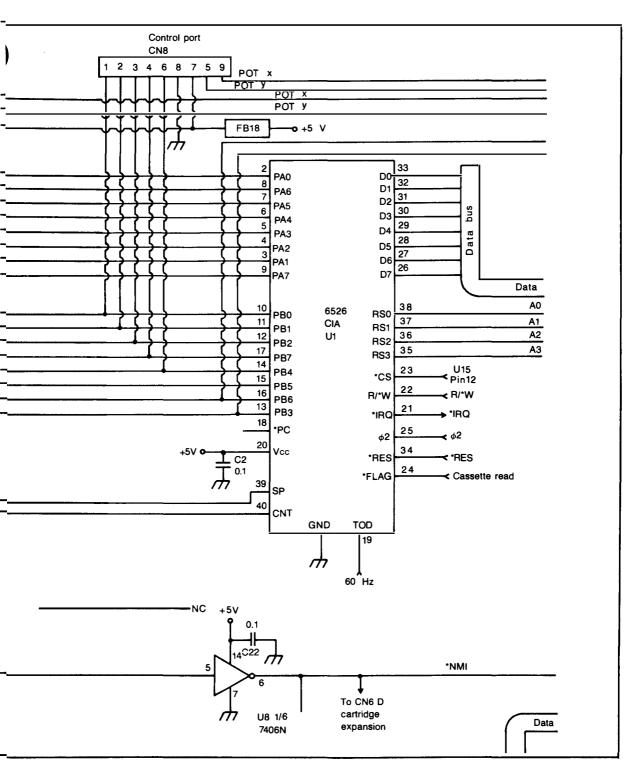

The input ports are on the extreme left side of the board in Fig. 1-10. There you'll find two 40 pin chips. They are both numbered 6526 and are called CIAs for Complex Interface Adapters. The leftmost one is connected to a plug that goes through a bundle of wires to the keyboard. It is the keyboard's port of entry. It also connects through the print

Fig. 1-8. At first glance the print board of your 64 can look like a jumbled mass of components.

Fig. 1-9. This block diagram shows how the chips in the 64 interact.

board to the joystick input plugs. When a key is struck or a joystick is moved the signal is transferred to the CIA and CIA places the signal onto a group of eight parallel copper traces called the data bus. The data bus transports the signal to the microprocessor further down the board.

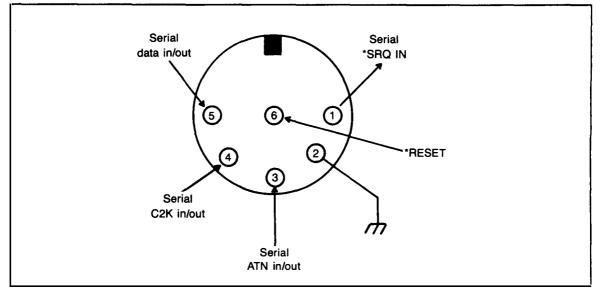

The other CIA is connected to the nearby user port and the serial port. The CIA performs like the keyboard CIA on the user and serial ports. It will receive the port inputs. In addition, it is able to output to these ports. The keyboard and joysticks, in contrast, use their CIA as an input only device. This CIA also is able to put the signal out on the data bus. It receives data from the processor on the bus.

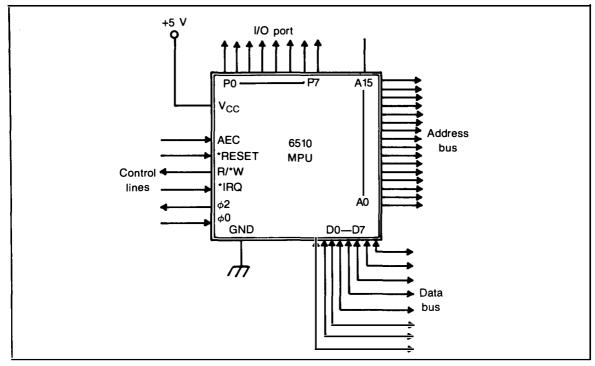

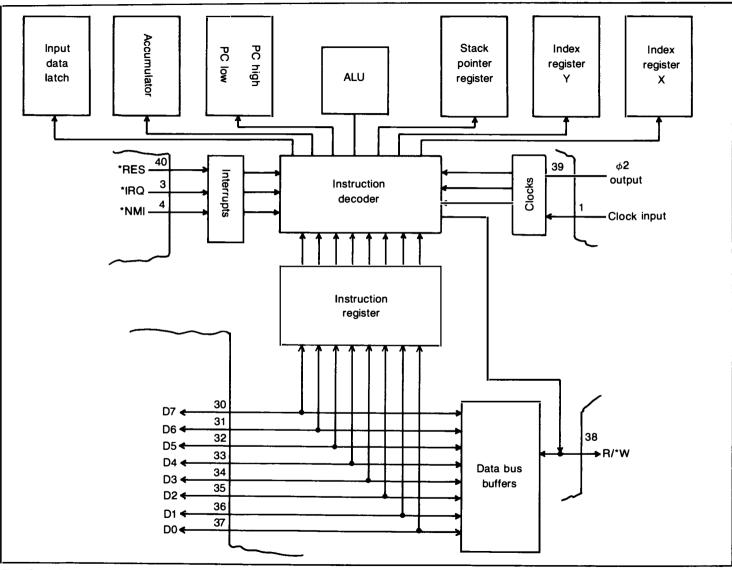

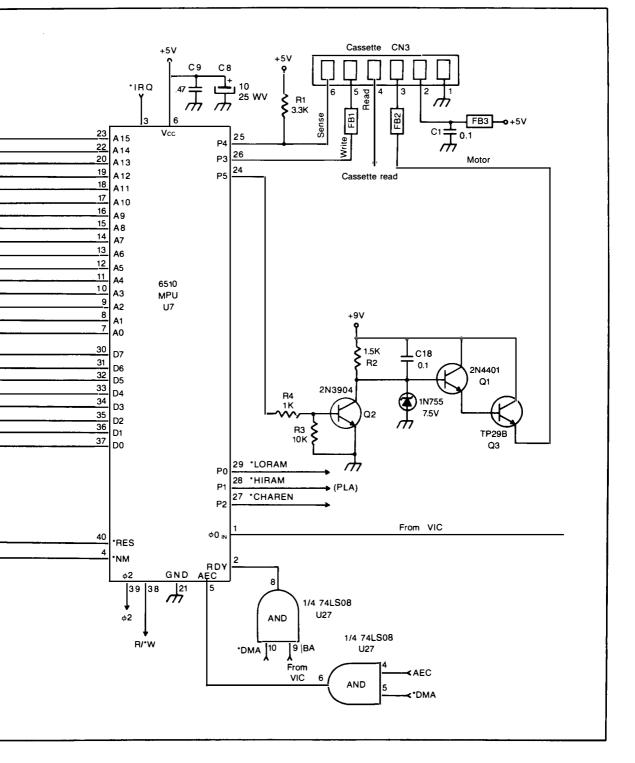

#### Microprocessor

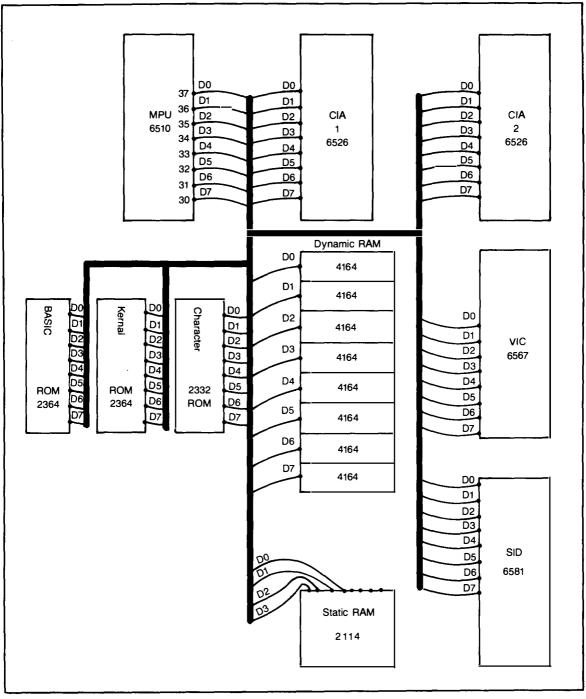

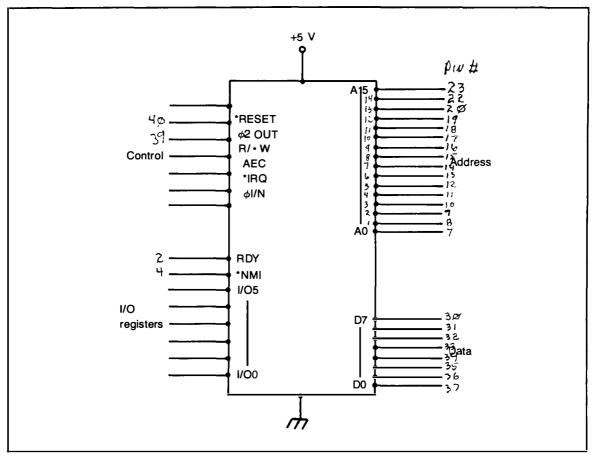

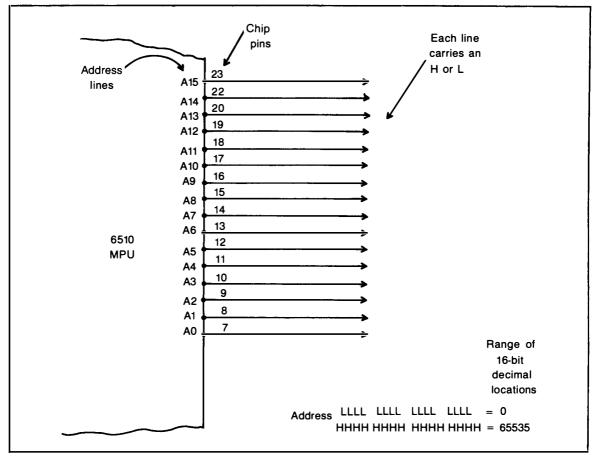

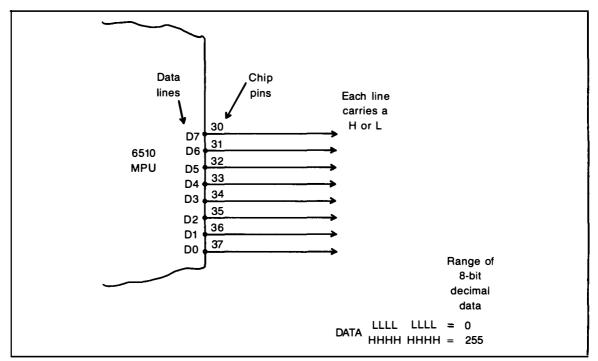

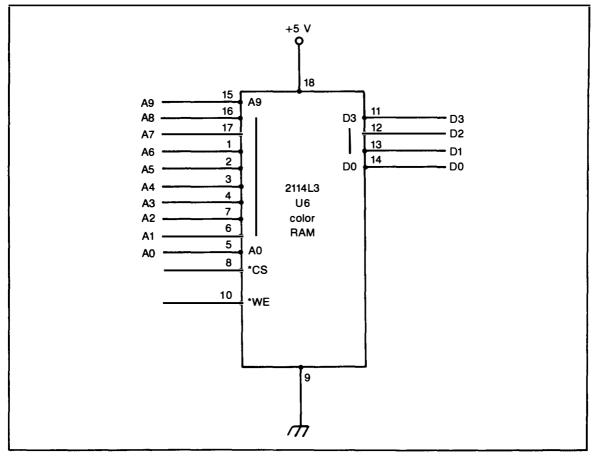

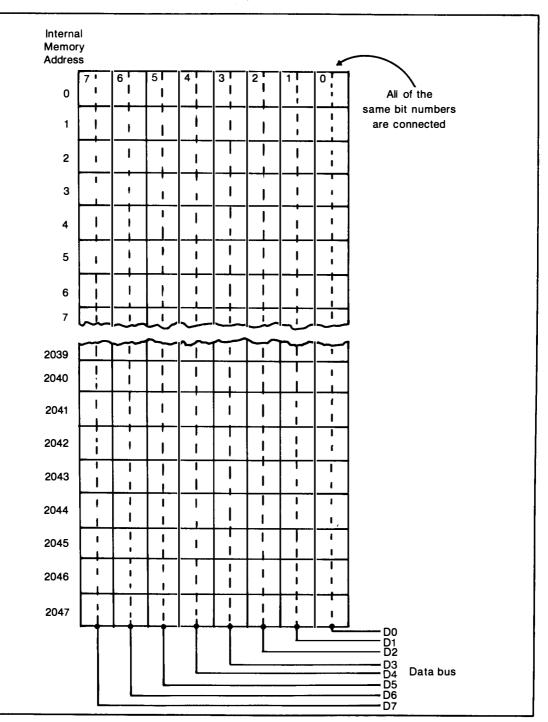

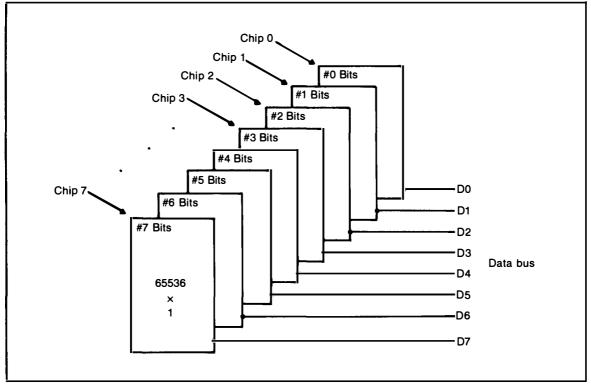

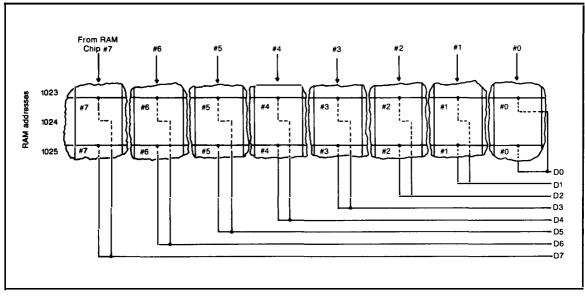

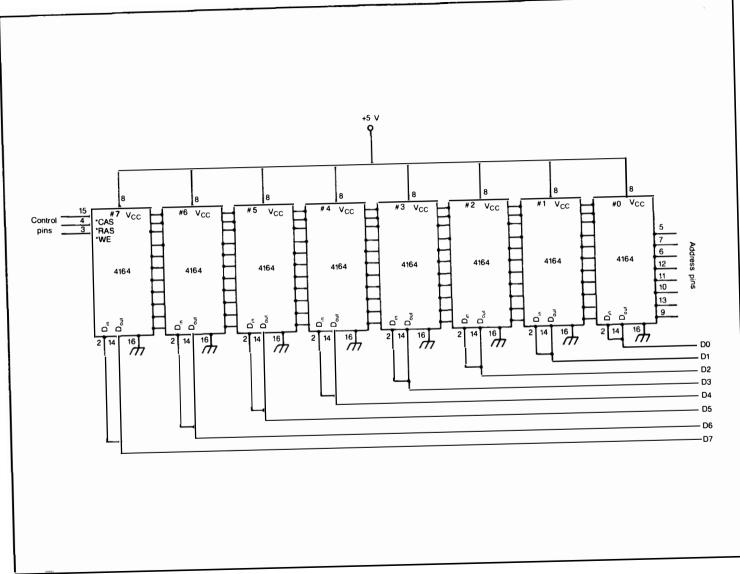

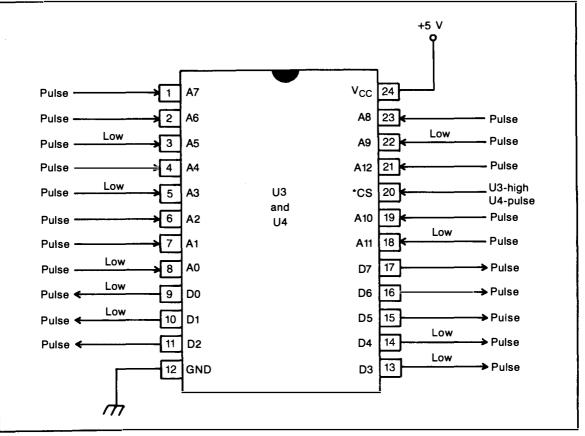

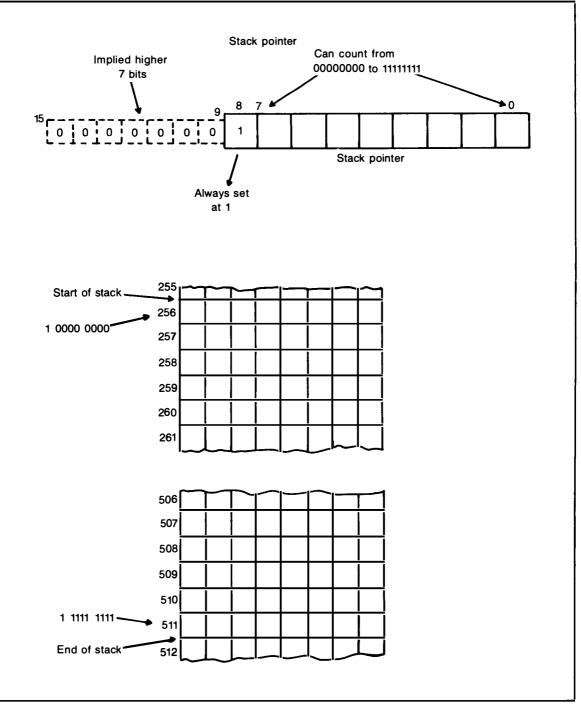

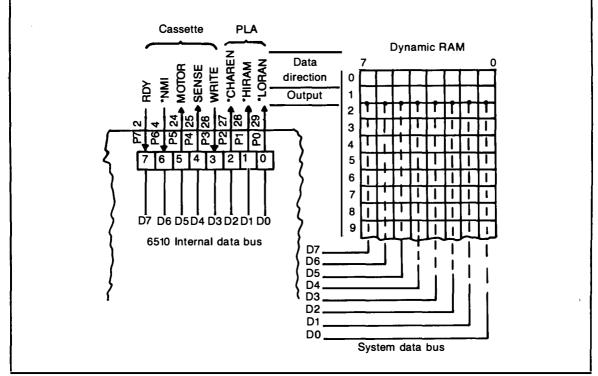

The processor is a 6510. It sits in the center of the board. It is the originator of the data bus. Besides connecting up to the CIAs via the data bus, it also hooks up to a number of other chips, as seen in Fig. 1-11. The data bus is sent to eight 4164 RAM chips, three ROMs, a 2114 RAM, the VIC,

Fig. 1-11. The eight lines of the data bus originate in the MPU. They are named D0 through D7. The CIAs, ROMs, VIC, and SID are connected to all eight copper lines. The static RAM chip attaches to only the four lowest numbered lines. The eight dynamic RAM chips each connect to a different one of the eight lines. The lines are all bidirectional.

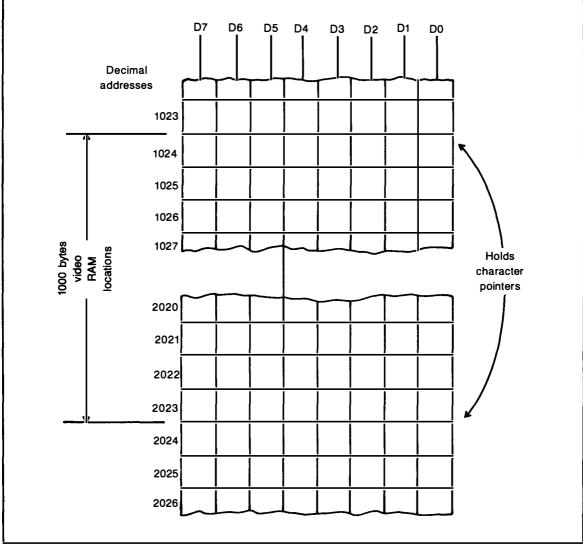

and the SID. All of the chips that the data bus is connected to have a decimal number that identifies specific locations. The numbers are called addresses.

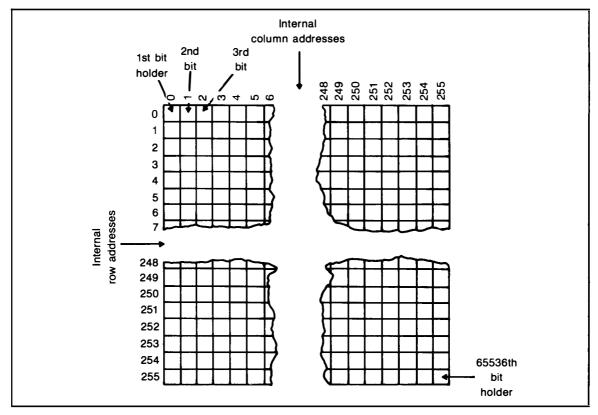

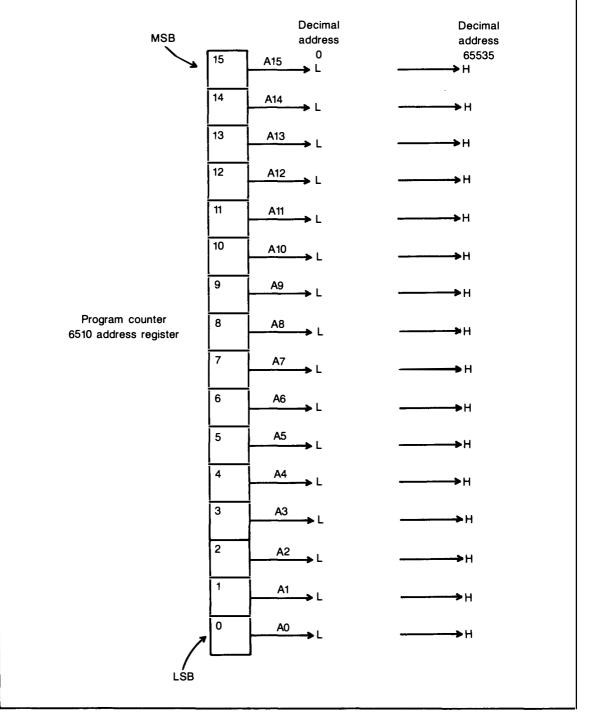

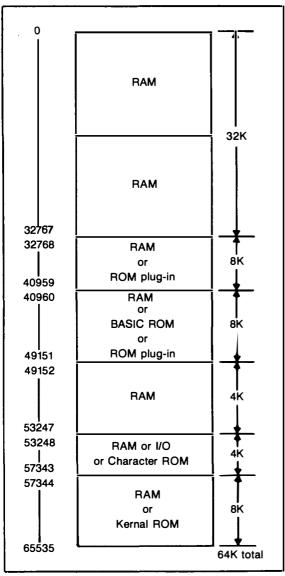

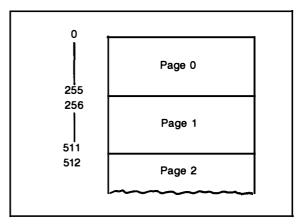

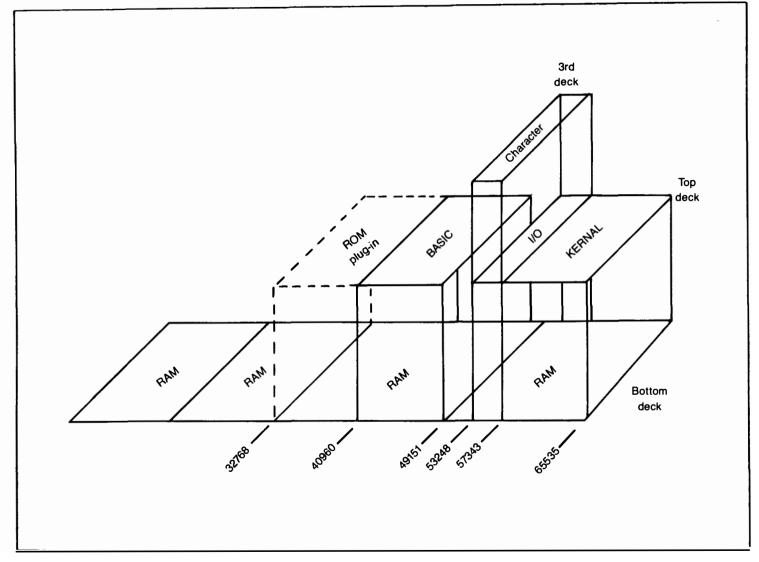

The addresses range from 0 to 65535. Each address can be accessed individually. All of the addresses connect to the 6510 microprocessor. A listing of the addresses and what the address is connected to is called the Memory Map.

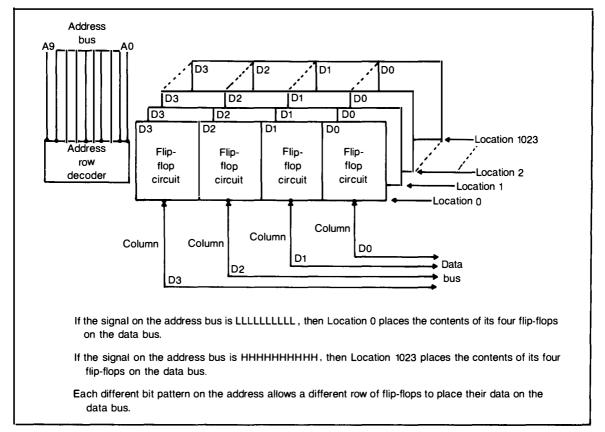

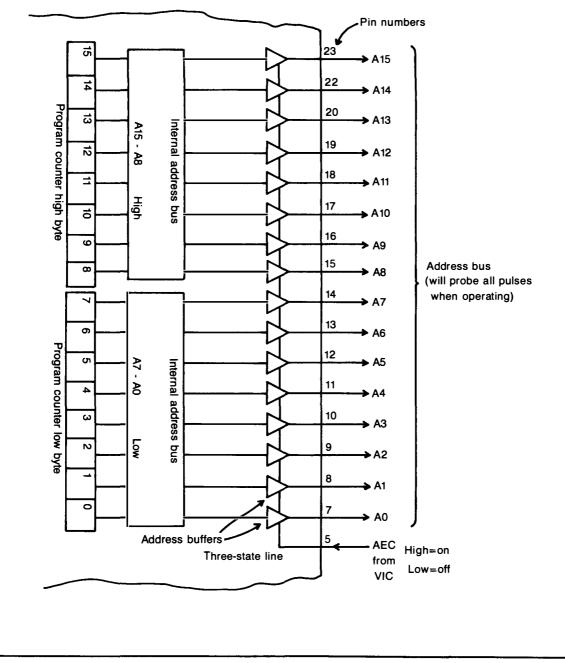

The processor can access the addresses through 16 copper traces called the address bus. It travels around the print board from chip to chip. The processor is able to place combinations of 16 highs and lows onto the address bus. There are 65536 possible combinations of highs and lows that can be placed on the address bus. Starting with address 0 and ending with address 65535 there are 65536 individual addresses. There are only a couple dozen or so chips, but the chips contain a lot of registers. Some of the chips contain thousands of registers. Each register has its own address.

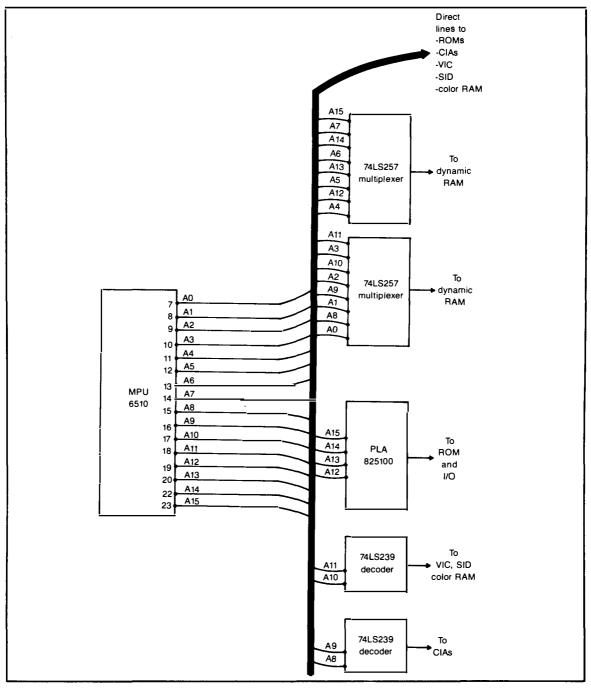

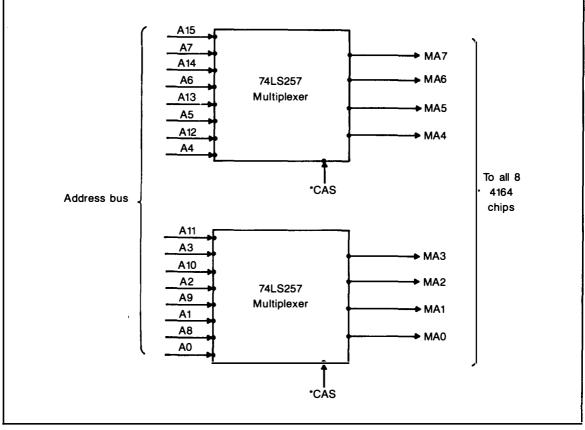

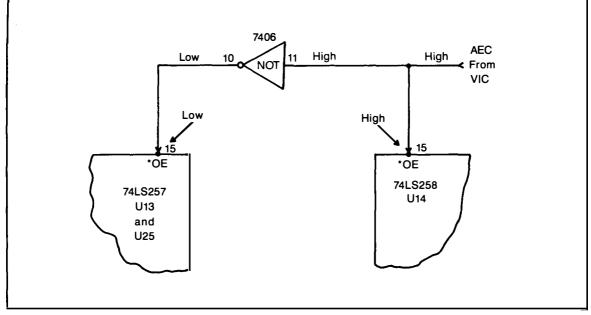

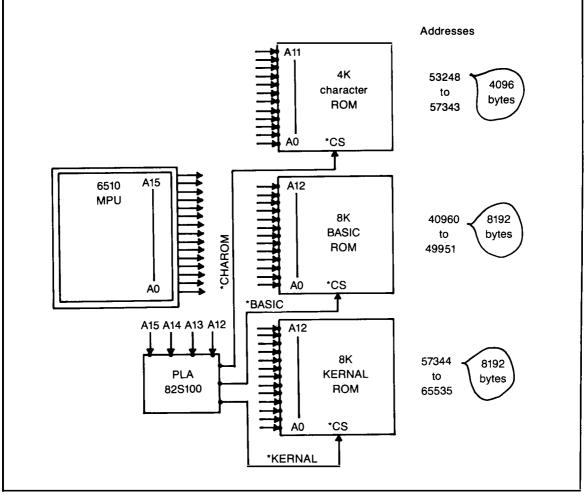

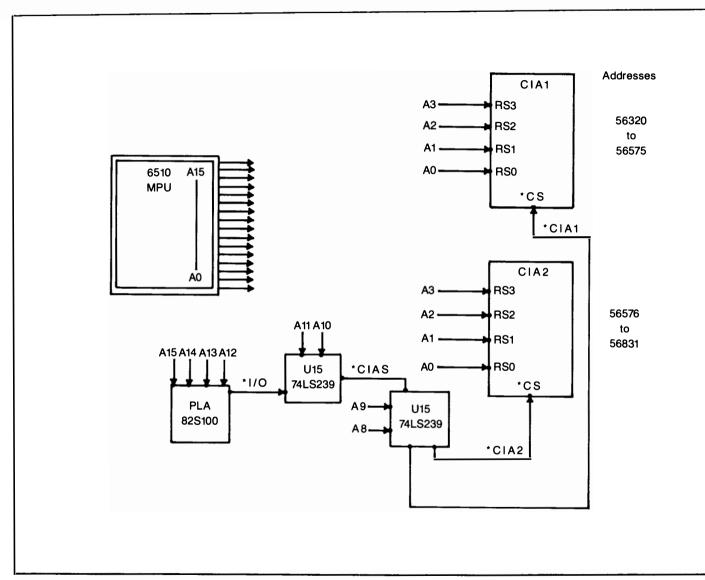

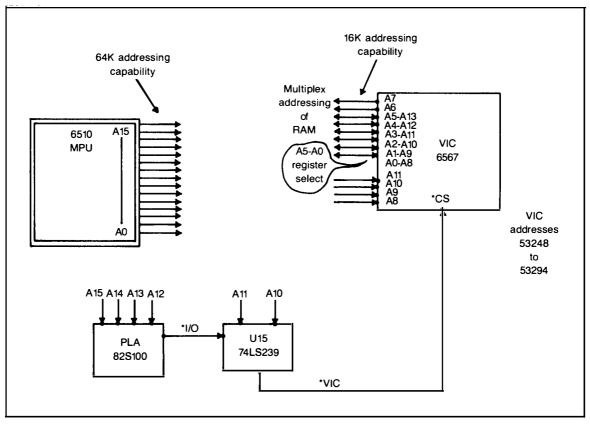

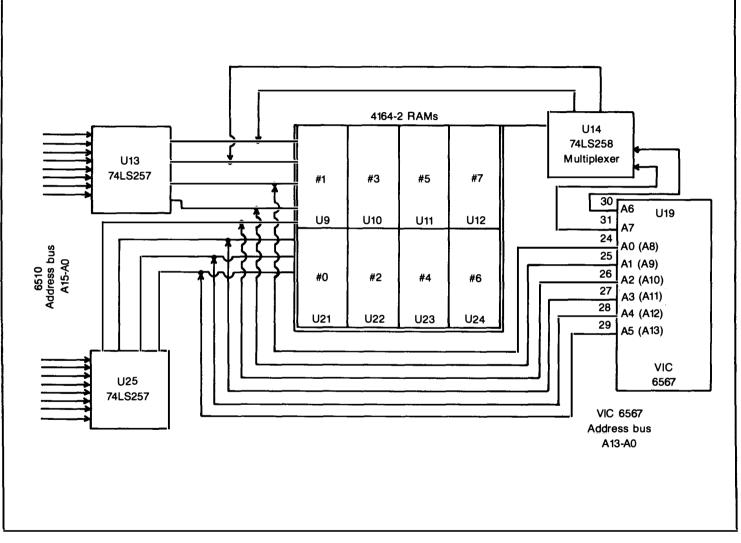

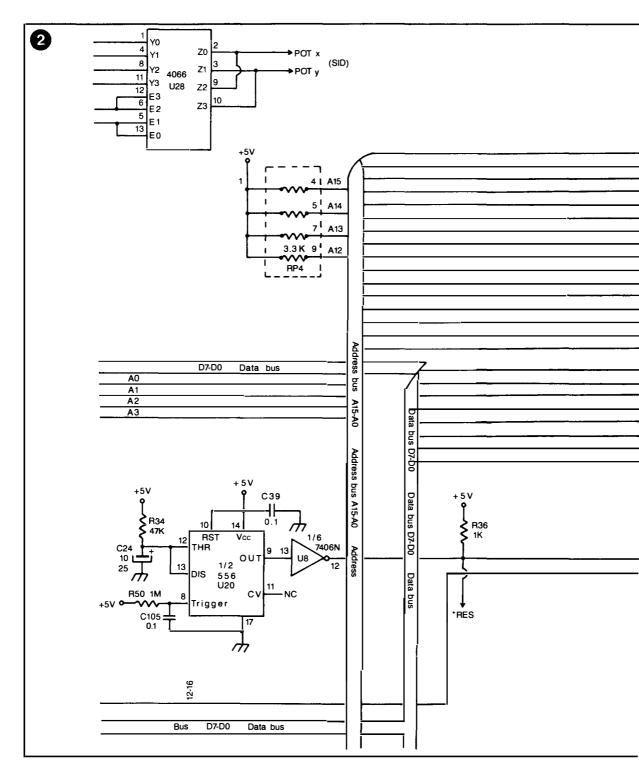

When the 6510 dials an address, all of the highs and lows do not go directly to the address. Some of them travel first to substation type chips called multiplexers and decoders. There are two 74LS257 multiplexers to handle the RAM addresses. An 82S100 PLA chip conducts the ROM decoding. Two 74LS239 decoder chips do the CIA, VIC, SID, and other decoding. The address decoding is shown in Fig. 1-12.

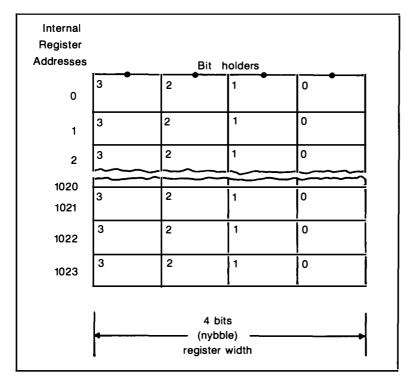

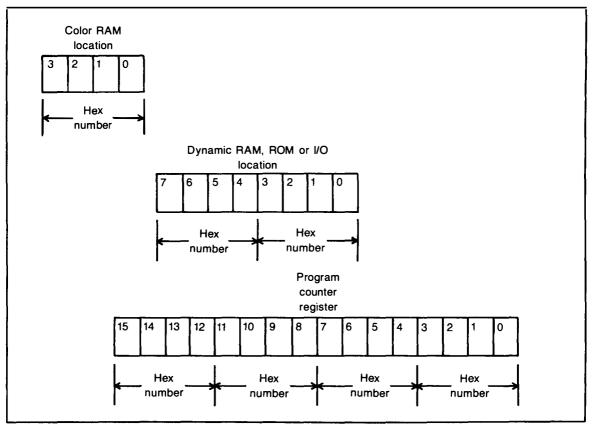

Once addressed, the location can then be either read or written to over the data bus. The reading and writing takes place as the 6510 sends eight highs and lows to an address during a write or receives eight highs and lows from an address during a read. All of the locations, except those on the color RAM chip, consist of eight bit registers. The color RAM registers only have four bit holders.

An eight bit register can hold a binary coded number from 0 to 255. There are 256 possible combinations of highs and lows in eight bits. As you no doubt know, eight bits make one byte. A four bit register can hold a number from 0 to 15. There are 16 possible combinations of highs and lows in four bits. Four bits make one nybble. All of the registers in the memory map are byte size except for the color RAM which holds nybbles.

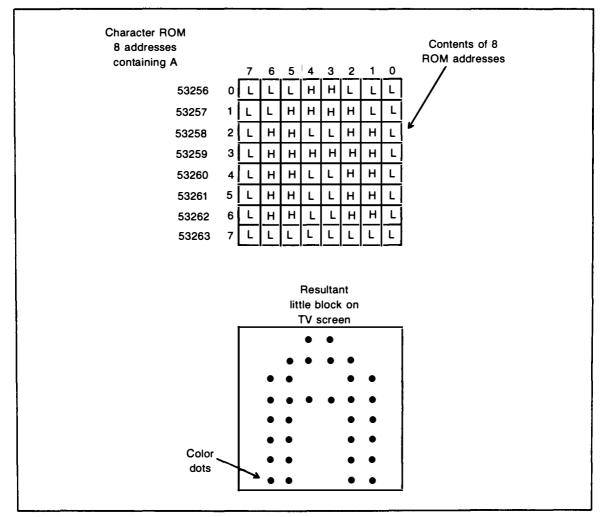

When you POKE data to an address, such as POKE 1099,65, the first number 1099 is a RAM address. The second number after the comma is the code for the byte LHLLLLLH. The byte is installed in address 1099. As it turns out, 1099 is a location in video RAM. If you POKE any bytes into video RAM, the VIC reads the byte as code for a symbol. The VIC then fetches that symbol from a ROM chip and displays it on the screen. If you POKE that number into video RAM you'll see a symbol replace the last asterisk in the top sign-on line. Try it. This development will be covered as you proceed in the book. If you are curious, the location could be probed with PRINT PEEK(1099). Your 64 should print 65.

The processor traffics with the chips in these ways. It sends and receives highs and lows over the data bus with the 4164 RAM chips. It receives but does not send to the ROM chips. It sends and receives data to and from the VIC and the SID.

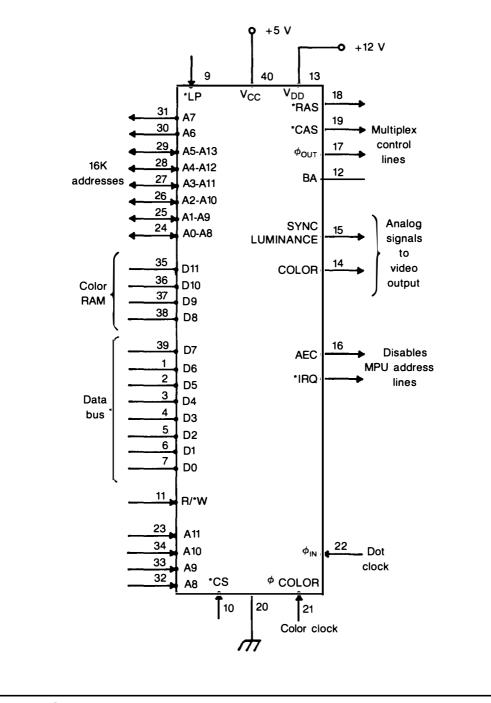

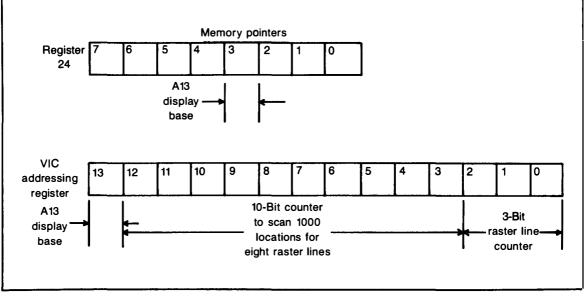

## Video Interface Chip

The VIC plays an unusual role. It is not only a resident of the memory map and is addressed by the 6510 in normal fashion, but it also can take over and act as the addresser. It is able to address more than 16000 of the total addresses. If any of the chips have addresses in the VIC's 16K range, the VIC can access the chip and read bytes of data out of it. This important VIC ability is covered in detail in Chapter 17.

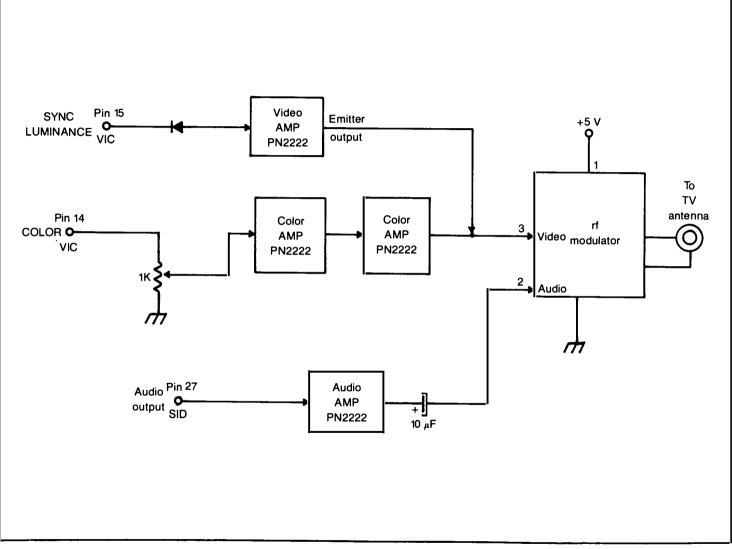

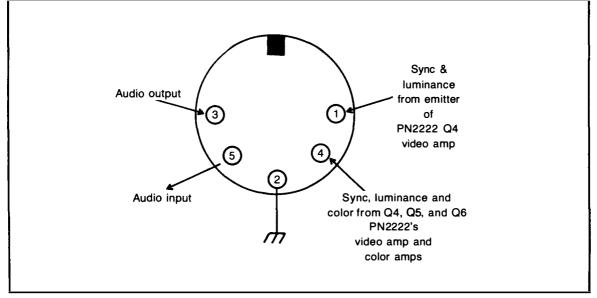

The VIC does not need an I/O port chip. It handles its own outputs. It does not have a provision for any video inputs. The VIC is the manufacturer of the composite color TV signal that is drawn on the face of the TV.

The 64 comes equipped with an rf modulator that makes the VIC output into a channel 3 or 4 TV compatible signal. The modulator is contained in a metal case and is located at the right rear of the print board. To the right of the modulator are power supply components including the power input plug, the off-on switch and the power fuse.

Fig. 1-12. The 16 lines of the address bus originate in the MPU too. They are named A0 through A15. The A15-A8 address lines are used quite a lot to select the chip that the MPU wants to contact. The A7-A0 address lines can be used to choose among the thousands of locations on the selected chips. The address lines go from the 6510 to the memory address locations.

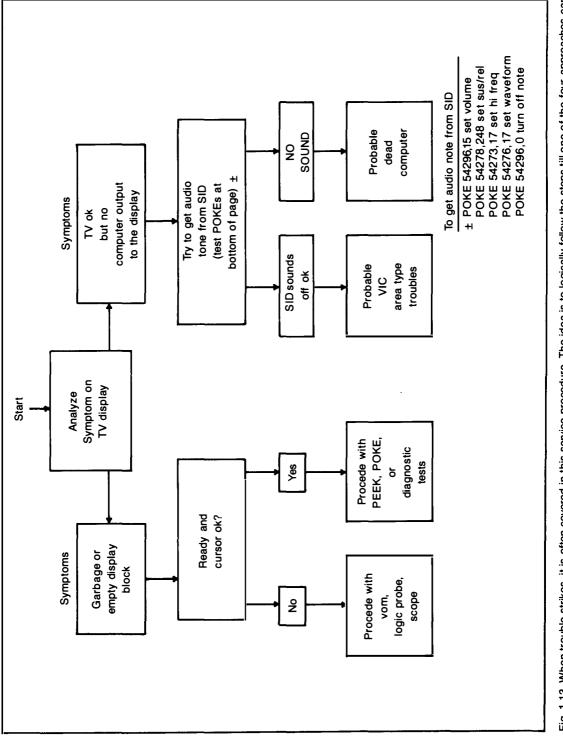

Fig. 1-13. When trouble strikes, it is often covered in this service procedure. The idea is to logically follow the steps till one of the four approaches can be confidently begun.

| Symptom                                  | Possible<br>Defect | Тгу                           |                        |

|------------------------------------------|--------------------|-------------------------------|------------------------|

| Disk won't work                          | CIA2               | Replacing chip                |                        |

| Printer stops                            | CIA1/CIA2          | Replacing chip                |                        |

| Keyboard won't work                      | CIA1 or            | Replace chip or               |                        |

|                                          | Keyboard           | repair or replace<br>keyboard | Table 1-1. Peripheral  |

| Modem not operating                      | CIA1/CIA2          | Replacing chips               | Troubleshooting Chart. |

| Audio-Video port<br>loses sound          | SID                | Replacing chip                |                        |

| Audio-Video Port<br>Ioses video          | VIC                | Replacing chip                |                        |

| Cartridge port not<br>operating properly | PLA/Kernal         | Replacing chips               |                        |

| Control port inoperative                 | CIA1               | Replace chip                  |                        |

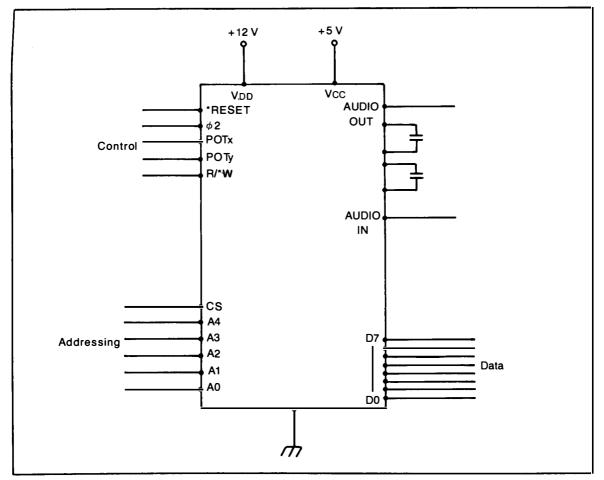

#### **Sound Interface Device**

The SID is the composer of the audio signal that the 64 puts out. The SID is also able to receive an audio input and process it along with sounds of its own. Like the VIC, it handles its own I/O without the aid of an I/O port chip.

#### **TROUBLESHOOTING CHARTS**

When a trouble occurs with your 64 and you realize it is being caused by the computer and not one of the external devices, refer to Fig. 1-13. If a device is at fault refer to Table 1-1. The first step is to analyze the symptom on the TV display. If the display is just a snowy TV picture, try a regular TV channel. Should the TV program be normal, move to the next block on the right side of Fig. 1-13.

Now the computer could really be dead and need power supply repairing, or the VIC could have died. To determine which section is at fault, try to produce a sound out of the SID. If the SID is quiet, then the power supply is indicated. Should the SID sound off though, the computer is ok except for the VIC and it's surrounding circuits. Turn to Chapter 18 for a SID test program of POKEs. If the sound test fails, then the power supply is suspect. Turn to Chapter 20 and follow the step-by-step instructions.

If the TV channel is also snowy, your TV is bad and you need TV service, which is not covered in this book. The same goes for any other recognizable TV problem. The computer is not the problem in these cases.

When the screen fills with garbage or comes on with an empty display block (the left side of Fig. 1-13), all of the digital circuit components are suspect. This includes the processor, RAM, ROM, CIAs, and decoders. The VIC and SID are probably not involved in the trouble.

When these symptoms occur, the READY sign and cursor might or might not be displayed. If they are not displayed, then diagnostic software cannot be used. The repair will begin by making voltage, logic probe, and scope tests. When the READY sign and cursor do appear, chances are you can make use of the various diagnostic PEEK and POKE tests or longer programs, as demonstrated throughout the book. W HEN A COMMODORE 64 GIVES UP THE ghost and you make the decision to repair it, most of the time you have to take it apart. The first time you do the disassembly you are sure to be hesitant. You know from long experience with all types of machinery that you could possibly cause some additional troubles just by taking it apart. You don't want to start a repair job by causing more trouble.

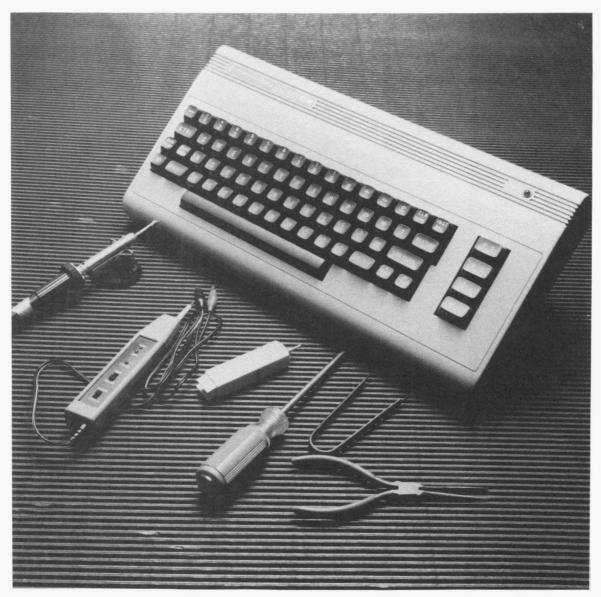

Fortunately, the 64 is assembled in a sensible manner, which makes the disassembly relatively easy, although extreme care and slow moves are the order of the day. The first steps are common sense. Arrange a large enough place on your work bench. Gather your tools together. Be sure to have good bright lighting and place a rubber mat on the bench. Disconnect all the attachments to the 64. Place it on the soft mat. Figure 2-1 illustrates your progress to this point.

It is a good idea to have the bench area as clean as possible. Dirt and filings that manage to enter the computer could cause troubles. It is not a good idea to work on the 64 in a low humidity environment. Should it be cold outside but nice and warm inside and static electric sparks are popping as you walk on the carpet, be careful about working on the computer. Chances are good you could blow out chips with the static activity. There will be more about the static electricity danger in Chapter 4.

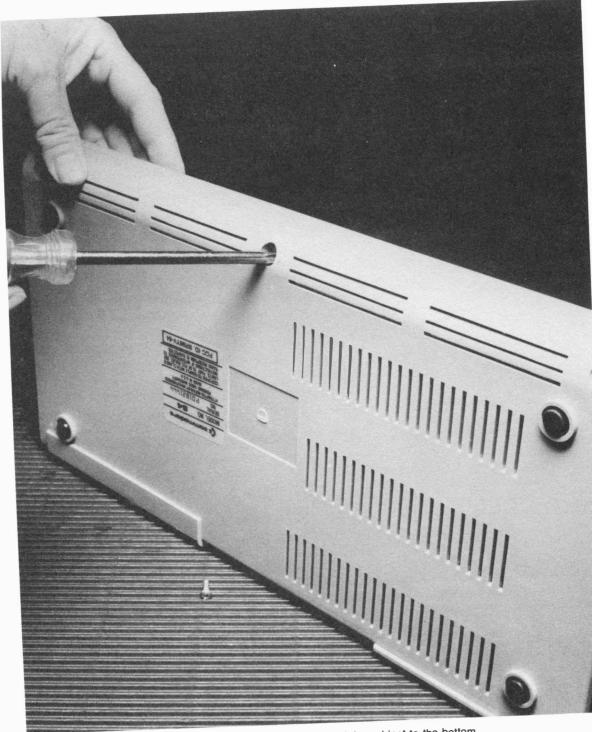

# REMOVING THE TOP

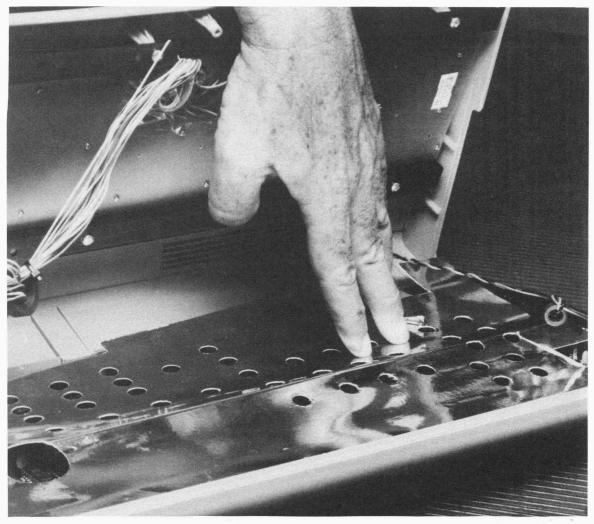

Place the 64 upside down on the soft pad. Position the 64 with the rounded front facing you. In the bottom of the case, there are three recessed screws along the rounded front. Take a medium sized Phillips head screwdriver and unscrew them as shown in Fig. 2-2.

Once the screws are out, turn the 64 back to it's normal position. You'll find that the top will now swing up at the front. As Fig. 2-3 shows, the rear end is sort of hinged. I say "sort of" because the hinging is just the plastic top and bottom cut to hold on to each other. When you swing the top all the way up, the hinging will disconnect and the top piece of plastic disconnects from the bottom. However, you must be careful. There are two miniature

Fig. 2-1. The 64's case can be opened with a Phillips head screwdriver. The print board is removed with the aid of a soldering iron and longnose pliers.

wiring systems that connect the top casing to the bottom.

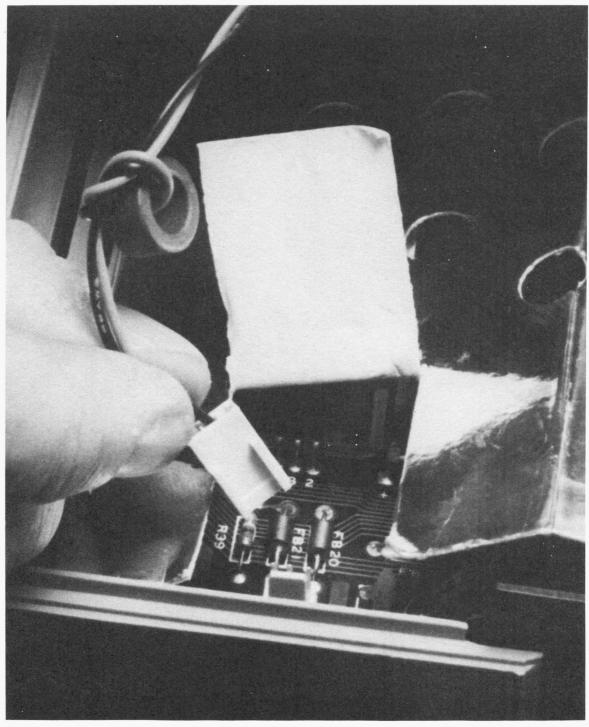

The first wires are three leads that connect the pilot light to the print board. You can remove it gingerly, as shown in Fig. 2-4, making sure you do not bend any connections or cause any damage to either end. The second set of wires are from the keyboard to the keyboard port. The keyboard port is a 20 pin male connector. The cable from the keyboard terminates in a 20 pin female plug as shown in Fig. 2-5. They can be pulled apart, but before you do, find out if it is necessary to disconnect them for purposes of repair.

In the 64, the keyboard is mounted firmly on-

Fig. 2-2. There are three Phillips head screws holding the top of the cabinet to the bottom.

Fig. 2-3. Plastic type hinging permits the top to be swung away from the bottom.

to the plastic case top. If you do not have to remove the keyboard from the top or unplug the 20 pin port connections, don't do it. The more you disconnect, the more you have to reconnect and the more exposure you'll have to possibly causing additional troubles. The good repairman only takes apart what is absolutely necessary. You can place the still connected keyboard to one side. Disconnecting the pilot light will give you plenty of room.

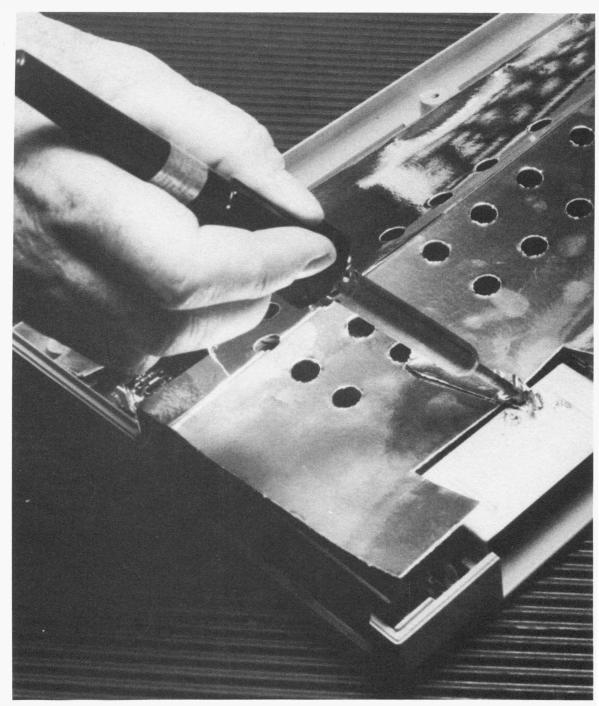

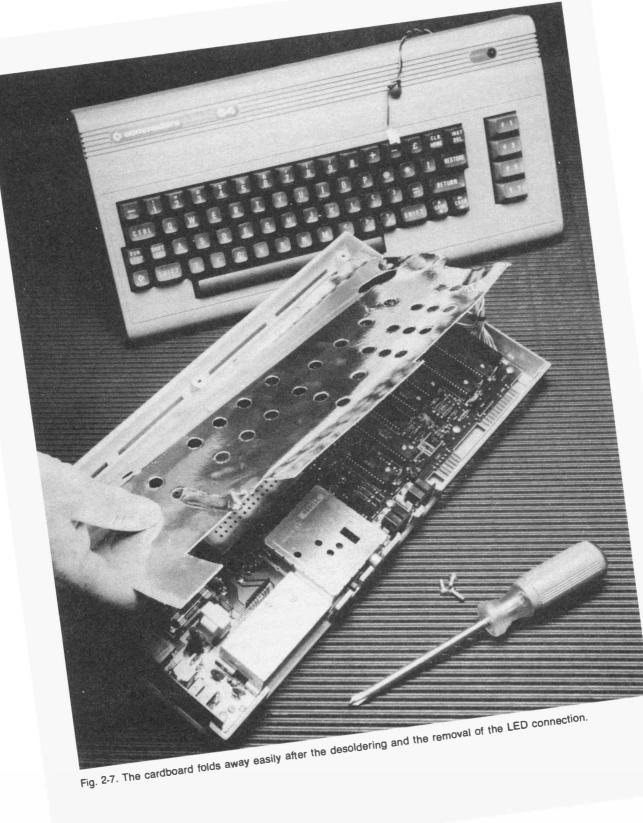

Once the top is to one side you'll be facing a piece of cardboard covered with silver foil that is hiding the print board. The covering is taped down to a shield on the print board. The tape is covered with a coppery cover and the tape is soldered to the shield in a couple of places. Figure 2-6 shows how to remove the print board cover. Desolder the tape with as little heat as possible. Then bend the cardboard back as shown in Fig. 2-7. That does it. You are into the print board area.

#### REMOVING THE PRINTED CIRCUIT BOARD

Separating the top of the cabinet from the bottom is easy. Three screws, a pilot bulb connection, one

Fig. 2-4. The LED Pilot bulb is connected to the board with a small pressure connector.

Fig. 2-5. The keyboard is plugged into a socket at the end of the print board.

Fig. 2-6. The metallized cardboard covering on the board is soldered to the cover of the rf modulator. It is removed with a low-wattage iron.

solder joint, and the job is done. Removing the print board from the bottom of the cabinet is somewhat more difficult. Fortunately, most repair jobs do not require the removal of the print board. When the job does dictate the complete separation though, here is how it is to be done.

First of all, the keyboard must be disconnected at its plug near the end CIA. The top can then be separated from the bottom. Place the keyboard top in a safe place. It should be clear of any undue heat and away from any liquids. If it is going to be disassembled for any length of time, box it or do something to keep it free of dust.

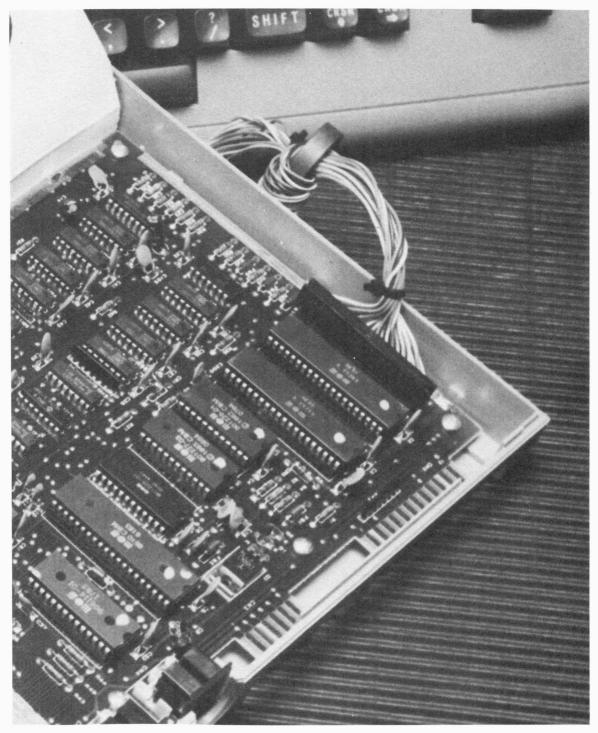

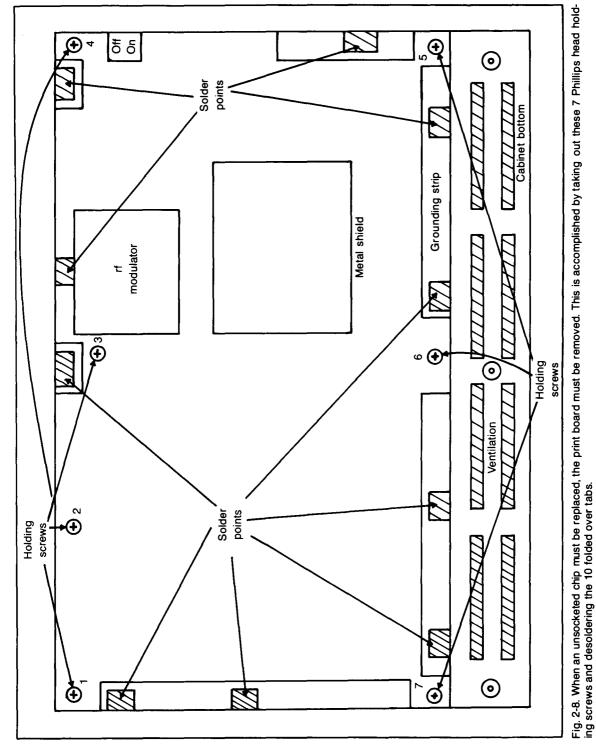

Figure 2-8 shows the print board screwed and soldered onto the cabinet bottom. There are seven Phillips head screws holding the board tight. Remove all of the screws shown without touching any nearby chips or ports. Keep the screws with the three you took out to open the case. These seven screws are a little smaller than the three for the case.

Once you remove the seven screws, the board can come free. If you grasp the board by the rf modulator, you can lift it right out of the cabinet. You'll see seven little plastic mold holes where the screws had been attached to the cabinet floor.

On the bottom of the board, you'll find a shiny metal cover. This is the ground plane. A closer look shows a tan sheet of insulation between the board and the ground plane. It keeps the board bottom connections from shorting to the ground plane. Notice the ground plane has a number of tabs that are folded over and connected to the print board grounding strip. There are ten tabs, and they are soldered to the grounding strip.

The rest of the disassembly job is desoldering. If you must gain access to the bottom of the print board you will have to desolder the ten ground plane tabs from the grounding strip. That will undo the sandwich of print board, insulator and grounding plane.

The desoldering is a tedious job and you must take care not to apply too much heat or pressure. The only reason that you would take the sandwich apart is to replace chips that are soldered onto the print board. There are 32 chips on the board of various sizes and shapes. Of the 32, eight of the largest are plugged into chip sockets. There are 24 smaller chips soldered into the board. If you must replace one of them, the sandwich must come apart. If you count the visible chips, there are seven in sockets. The eighth one is under the metal shield. To open the metal shield, take a small screwdriver and turn it in the notch on the left side. The top of the shield is hinged and the notch is where it opens.

There is one more socketed chip under the shield along with four smaller chips that are soldered in place. The socketed chip is the VIC. When you open the shield, note that the VIC has a heat sink that touches the shield. The sink is covered with a white silicon paste to conduct the heat away from the VIC. Should you replace the VIC be sure to reapply the silicon paste.

It is vital that, as you take apart the 64, you perform the disassembly in a slow and deliberate manner. Carelessness will result in "induced" troubles. That is, troubles caused by you. If you disassemble correctly, then you'll be able to get it back together again without undue difficulty.

#### **DISASSEMBLY AS A CURE**

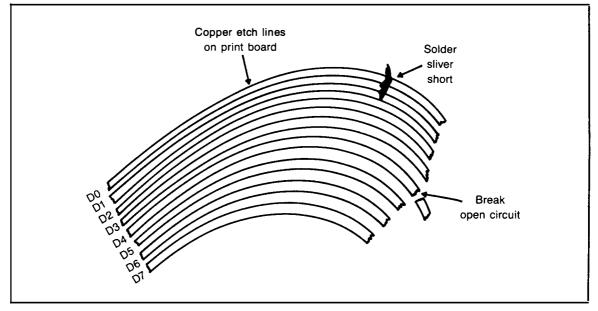

The step-by-step procedure of disassembly often provides a fix all by itself. Sometimes during print board manufacturing, a form of booby trap can be accidentally installed on the board. After the print board is assembled, it is typically soldered with automatic machinery. During the soldering process, the machines generate hot gases that can expand rapidly and shoot liquid solder into the air. As the solder cools and falls, it hardens. The solder then forms little balls and drizzles down onto the board. The little balls have flux on them and often will stick where they hit. They are tiny little troublemakers.

Of course, the factory is very aware of the solder drizzle, and the board goes through an extensive cleaning procedure after soldering to eliminate this potential source of trouble. However, no matter how hard they try an occasional sliver of solder will stick in a place where it is not seen but does

. .⊑ 25 not cause any trouble at that time. It sneaks through the extensive board inspection and is shipped out with the finished computer.

Somewhere down the line, as the computer is taken home and put into service, a solder ball gets loose and starts rolling around the print board. It settles into a spot such as between two pins on the CPU. The computer stops operating in a logical manner. A screenful of garbage appears. The computer needs service.

If this happens to you and you have had the computer more than the limited warranty time of 90 days and you decide to check it out yourself, the first thing you do is take it apart. As you remove the casing and turn the board over on its side, a tiny solder ball could plink out. Then when you attach power and turn it on, the garbage is gone! The computer is now working fine. Yes, you have completed a fix. The removal of the solder ball short has cured the trouble. The technique was simply taking the computer apart.

#### VISUAL INSPECTION

While the solder ball type of short does happen on occasion, most of the time you are not so lucky. There are, however, a few other service moves that are easy to make that do often produce good results. First of all there is the visual inspection.

The first step of a visual inspection is to take the computer apart and expose the print board. This includes removing the metal shield over the VIC after you have inspected the open areas of the board and found nothing out of the ordinary.

To inspect the board, a bright light and a good magnifying glass are very helpful. You are mainly looking for short circuits, open circuits, and burnt or mangled components.

#### **Ground Plane Short**

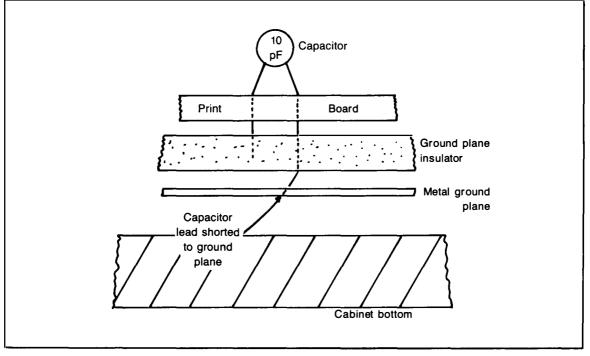

One common short happens when a chip lead pushes into and punctures the insulation between the print board and the ground plane the board is

Fig. 2-9. The print board is the top of a sandwich. If a component lead should pierce the insulator, in the middle of the sandwich and contact the ground plane, the bottom of the sandwich, a short circuit could develop.

Fig. 2-10. The bus lines are copper-etched wiring strips that traverse the board. A short or open line will cause trouble.

mounted on. As shown in Fig. 2-9, the computer is put together in layers. The cabinet is at the very bottom. The metal ground plane is against the cabinet. It acts as a common ground for the entire board as well as a shield to ward off interference that might come up through the bottom of the machine.

The insulator is on top of the ground plane. Its job is to keep all the active connections in the board from contacting the common ground. The print board is mounted on top of the insulator. A ground plane short occurs when one of the print board active connections manages to puncture the insulator and make contact with the ground plane. You can often spot the short and clear it by snipping off the excess amount of the lead or by bending it over.

#### **Board Defects**

Another quick check should be made at the chip sockets. Sometimes a socket pin can get bent under instead of being soldered into its board hole. It could also sneak by inspection as it works ok since the socket is attached firmly and the bent over pin makes a pressure contact. However, in your home, after about a year, some corrosion builds up on the pin and the pressure contact no longer holds. You suddenly have either loss of computing or erratic performance.

This type of trouble can be seen with the bright light and magnifying glass. Once you locate it, you can gingerly move the pin into its appointed hole and apply a tiny drop of solder with a small iron.

Other types of board defects can also be found visually. The 16 copper address lines that travel around the board from chip to chip and the eight copper data lines that take almost the same routes as the address lines should be examined carefully. These two bus lines must be continuous. There cannot be any breaks. Also each line must be separate. They are not allowed to touch. If you find a break, then you have an open circuit. If any of the copper traces touch each other, then you have a short circuit. Figure 2-10 shows both problems. Either way, you are going to have trouble. Chapter 15 goes into these bus lines in detail. It is good practice to examine the address and data bus lines carefully before each repair. Odds are favorable that you might find a solder sliver short or a break and have a quick fix.

#### **CLEANING**

Another service move that might complete a repair, but is useful in any case, is cleaning. While the computer is apart, you will be able to see how dusty it is. As a computer is used and time goes by, the inside collects dust. It can't be helped without taking extraordinary measures. Dust itself is not a problem. Ordinary dust is an insulator and, as such, won't short out the print board or its components. One problem, however, besides the fact that it is dirty, is ventilation. Dust enters through the ventilation slots. If enough dust collects, the circulation becomes restricted, which can cause some overheating. If dust gets into the keyboard area, the interface ports, or other moving part areas, it can clog up plugs and cause all types of annoying and erratic operation.

A good way to remove the dust is with the patient use of a thin, clean, dry paint brush. The dust removal should be done slowly and carefully. Be especially careful around the RAM chips since they are susceptible to static electricity. Don't dust on a day that is dry and static electricity is jumping off of you. It is a good idea to ground the brush in any case, as described in Chapter 4. Never use any water or cleaning solution on the board. The idea is not to make the board spotless. All you want is good air circulation and a clear view of the circuits.

#### STATIC ELECTRICITY

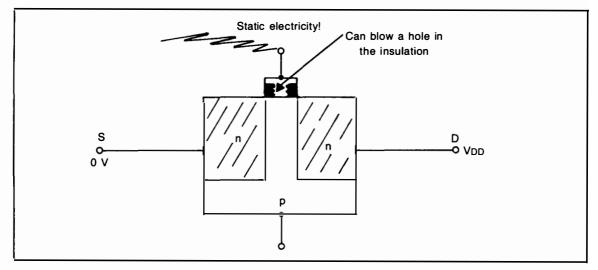

The silicon chip has one serious drawback. It can be easily destroyed by ordinary static electricity. If you walk across a carpeted room on a dry day, reach for a chip, and a static spark flashes from your hand to the chip, odds are the chip has just been electrocuted. Oftentimes, you cannot stop the static build up of the electric charge on your body. How can you avoid this problem? There are ways. Let's examine the situation first before discussing the preventive measures you can take.

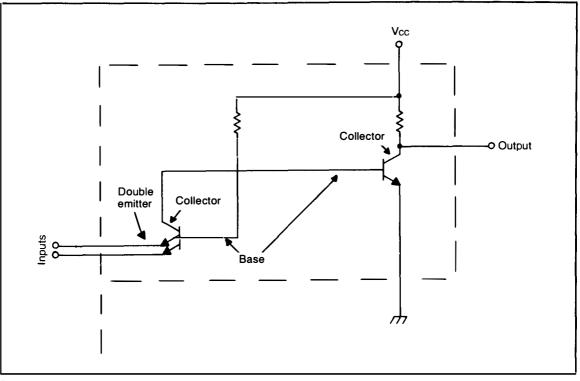

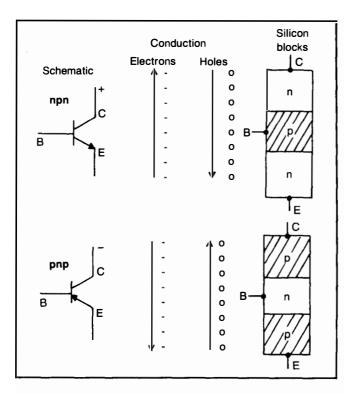

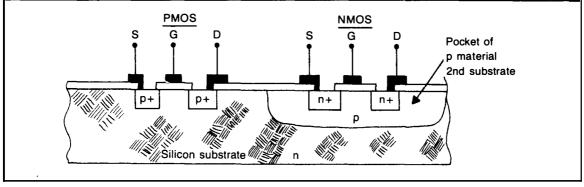

There are two important types of chips you'll encounter in the 64. One is called TTL, which stands for Transistor-Transistor-Logic. The second is the MOS, which stands for Metal-Oxide-Semiconductor. There is more detail on the construction of these chips in Chapter 4.

The chips have a lot of electrical characteristics. One of them is the amount of static voltage a chip can take before it is damaged. This is called the Threshold Voltage for Electrostatic Damage. It is measured in volts. It has been shown that a TTL will be destroyed if a static shot of 300 volts or more is allowed to contact it. The MOS chips are likely to fail if hit by 250 volts or more. How much voltage is pushing a spark between you and the door knob on a low humidity day? It could easily be a jolt of 3000 volts! As you can see, it is quite easy to kill a sensitive chip.

#### What Is It?

Static electricity involves the build up of electric charges on the surface of an insulator. The electric charges are electrons. The insulator will be charged if there is an excess or deficiency of electrons. An insulator with an excess of electrons is said to have a negative charge. When there is deficiency of electrons, a positive charge is present. The voltage developed gets larger as the charge increases. Either type of charge can cause a spark and a chip death.

Static electricity results from friction between different types of material. Your shoes on a carpet produce a lot of this friction. As you walk around the room, you charge up. The rug and your shoes are insulators. The charge is built up there and passed into your body, which is a conductor.

The charge on an insulator remains at the spot where it develops. The charge on a conductor, however, spreads itself uniformly throughout the conductor. That is how we are able to get rid of the charge. If we, as conductors, touch an earth ground, the charge is removed at once. However, keep in mind that the discharge to earth ground consists only of the electrons in our body. Any charges that are on our pieces of clothing, which are mostly insulators, will remain. Attention to chip handling must still be a concern even if you are grounded properly.

To alleviate the problem somewhat, wear clothes that are more conductive. For instance,

Fig. 2-11. In order to keep static electricity on your body at a harmless, low level, commercially available wrist strap systems can be used. They provide an escape path to earth ground for the unwanted charges. leather soled shoes are better than rubber soled shoes, and cotton clothing is more conductive than nylon.

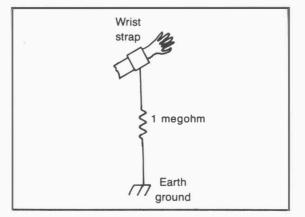

#### Wrist Strap

If you are going to be doing any extensive chip handling, the professional way to deal with static electricity is with a commercially available wrist strap discharger. These can be bought in an electrical or electronic supply house. They consist of a wrist strap that is a conductor with a connector coming out of it. The connector contains a resistor, typically about a megohm, that connects to an earth ground. Figure 2-11 illustrates this grounding scheme. Any charge that builds up in your body will immediately be discharged to earth ground. Note

Fig. 2-12. This chip extractor has a hole in the top to connect a ground wire to it.

that I said earth ground. A cold water pipe is usually such a ground.

This wrist strap is to be used only while you are working with equipment that is completely disconnected from any sort of electric power! While wearing the strap, you are connected to ground. If you contact 120 Vac, you could get a nasty electric shock, although the one megohm resistor will help to limit current. To be safe, only connect yourself to the wrist strap during chip handling on disconnected equipment.

Put the wrist strap on before opening up the computer. Keep it on all during any chip handling. You are producing static electricity with every move you make. Be sure to remove the strap before you plug in the machine to the line voltage.

#### **Additional Precautions**

The professional electronic technician often uses a lot of other static discharge techniques to avoid chip losses. First of all, work benches are usually insulators. They build up charges. You can't easily discharge the entire surface because a ground wire only discharges the point of the bench it touches. To solve this difficulty, the technician will ground the print board he is working on. Being sure the board is disconnected from power, he will connect a jumper wire, with a one megohm resistor in series, from the board to an earth ground.

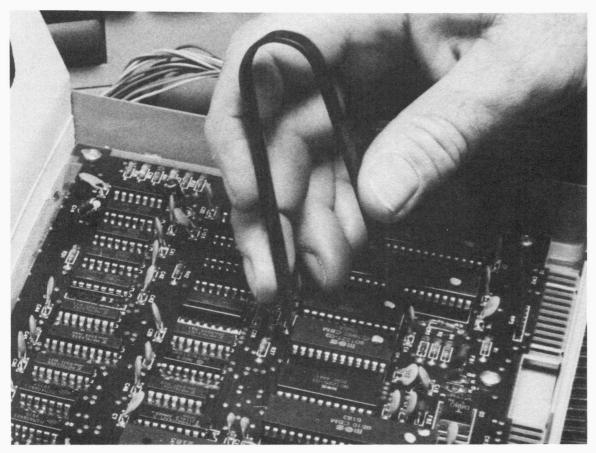

The replacement chips come packed in a conductive foam. He does not remove the chips from the foam till he is ready to install it into the print board. He will never take the chip out of the foam a long time before it is going to be installed and store it in a shirt pocket. That is asking for trouble.

If you can, it is a good idea to pull chips off print boards with a grounded extractor tool like the one in Fig. 2-12. The tool in the photo has a hole in the top to attach a ground wire to it. A companion tool is the chip inserter. It can also be conveniently grounded through the pin on its top.

You may think that I am overly cautious concerning these chip handling problems. It is possible and even likely that you could replace a chip without all these measures. However, if you do blow out a new chip with a static spark after waiting weeks for it to arrive, the feelings of frustration can be aggravating.

# 3. Chip Location Guide

T HE FIRST PIECE OF SERVICE INFORMATION a TV repairman looks for during a job is the TV's Location Guide. There is such a guide pasted on the inside or bottom of practically every TV. The guide is a rough layout of all the important landmarks in the TV. This includes any tubes, all the transistors and chips that the TV uses. The guide gives the location, name, and generic number of all the landmark parts. The servicer is usually able to complete most TV repairs with the aid of the guide coupled with his knowhow. I do not know of a single TV that comes purposely without such a location guide.

On the other hand, I have not seen a guide like this in any computer, including the Commodore 64. Therefore, since the last chapter provided the information on taking the 64 apart I will take the next servicing step and create a Chip Location Guide. I will place on the guide a lot more than just the 32 chips.

## **DRAWING A GUIDE**

This book covers the Commodore 64. As time goes

by, the model number could change and the layout of the print board might vary. I will use my 64 as the basis for the guide I'll produce.

All that is needed are some simple school supplies: a pencil, a ruler, and some graph paper. Drawing a useful guide shouldn't take more than five minutes. You will easily save more than that during any 64 repair or cleaning job with such a guide. There will be no stumbling through a complex factory drawing or schematic when the repair only requires knowing where the chips are. In addition, if the repair does need more servicing information than the chip guide provides, you'll already be briefed since you did the chip guide first. It will be much easier to read the complicated service information that you will be studying later in this book.

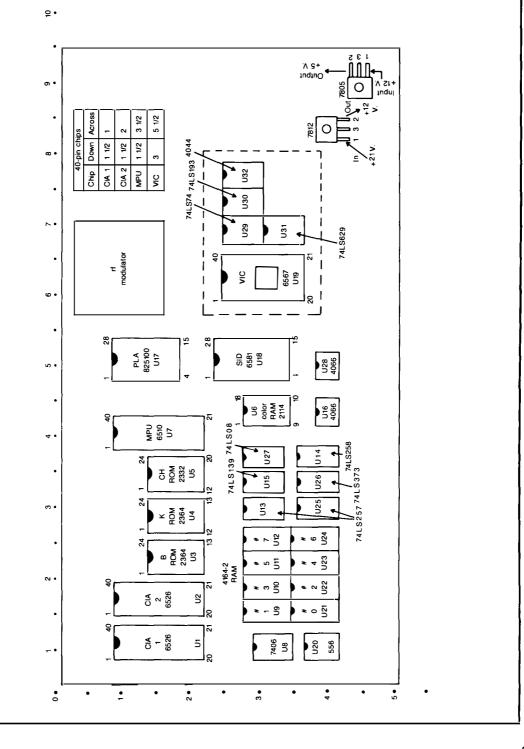

To begin, take a piece of graph paper about 8  $1/2" \times 11"$  and draw a rectangle about 5" wide and 10" high. The 64's print board has an aspect ratio of approximately 2 to 1. Lay out coordinates by inches. My illustration in Fig. 3-1 shows 10" across the top of the rectangle and 5" up the left side. That

way ever chip on the board has a location. For example, suppose you want to know where the 6510 MPU is located. All you have to do is look on the chart that accompanies the sketch. It says the MPU is located at 3 1/2" across and 1 1/2" down. A glance reveals the 6510 on the location guide and the chip is quickly found on the print board in the same relative position.

Once you have the coordinates laid out, you can draw in the chips. Do not worry about being exact. The only reason for the guide is to give you a feel for chip locations. You should have a familiarity of the board layout of any computer you are repairing or cleaning. The better your feel of the board, the faster and safer the work will progress. It is all in the interest of eventual mastery over your 64.

The shape of the chips can be approximate. The location of the chips need not be precise. You do not have to put the manufacturers part number on the chip. You do not even have to put as much information on your guide as I've shown in order for the guide to save you lots of time.

I put the following information into the illustration. First of all there are four 40 pin chips. There are three out in the open and the VIC chip encased in a metal shield. The 40 pin chips require a bit more care. I have a little chart for them at the top of the page. The chart quickly identifies them by their coordinates. I also identify them by their corner pins, function, and generic part number. For example, the VIC chip is shown as a 6567 in Fig. 3-1.

The 40 pin chips are drawn onto the chart first. In this case I've drawn in the two CIAs, the MPU and the VIC. Since the VIC is under a shield I've drawn the shield as a dotted line. The rest of the chips are then sketched in by using the 40 pin packages as reference. There are the RAMs, ROMs, buffers, latches, decoders, flip-flops, gates, separators, video circuits, the rf modulator, and finally the power supply regulators.

I'm sure it will take you longer to read the last few paragraphs than it will take you to rough out a useful location guide for the 64. In case you want to avoid actually drawing the location guide, make a photocopy of Fig. 3-1 and paste it inside your 64 case. You'll miss out on one pass at becoming familiar with the print board though, if you do copy it.

The amount of information required for the quick checks is actually small, and you have all these valuable tidbits on the guide. They are the location of the chips, corner pin numbers, the function of the larger chips, the generic part number, and the dc voltages in the power supply. With only these tiny bits of information, you can complete a large percentage of repairs in the same way that a TV repairman does using a tube and transistor guide.

Between Fig. 1-9 and Fig. 3-1 you can quickly refer to the following information:

$\Box$  The location of all the chips. If a chip has a paint dot or notch at one end, it is marked on the guide. Pin 1 will be found immediately to the left of the marking.

$\Box$  The location of the chips under the metal shield. The dotted lines could serve as a reminder to replace the shield after the repair. It is not good practice to leave shields off.

$\hfill\square$  The location of any and all plugs, adapters, and other interface circuits.

$\hfill\square$  The location of external circuits mounted inside the case. The rf modulator is an example.

$\Box$  A special marking to show which chips are socketed and which are not.

$\Box$  The location of the power supply fuse.

$\hfill\square$  The function of the large chips and their generic part numbers.

$\Box$  The voltages of the power supply regulators.

These two drawings illustrate what you actually see when you look down at the print board. It gives you the perspective of the physical computer. As you compare the guide to the board during troubleshooting and repair, you do not have to convert a theoretical schematic symbol to a physical layout as you must when the schematic is used for location information.

These guides, though, will only take you so far. They enable you to find a suspect chip so you can remove it from its socket and try a new replacement. They show you where the fuse and the

Fig. 3-1. The Chip Location Guide is the most used piece of service information during repairs.

various plugs are to check for visual indications of trouble. Fortunately, these few general checks will allow you to complete a large percentage of repairs.

When the simple measures fail and the repair does require the use of the schematic, the value of the location guide does not end. When you read the schematic, you are seeing symbols that represent the physical chips and other components. Yet the symbols and the actual components bear no resemblance to each other. You must be able to relate the symbols to the electronic parts on the print board. You'll find that the familiarity you gain with the location guide helps bridge the step of finding a part on the board after reading it on the schematic.

#### **CHIP SURVEY**

To get you even more familiar with the circuit board, I want to introduce some of the major chips that you have drawn on your chip location guide. I will locate each chip with the coordinate system used in Fig. 3-1.

#### Microprocessor

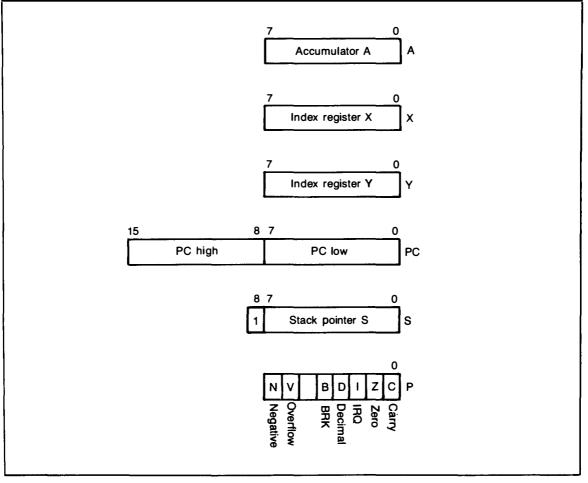

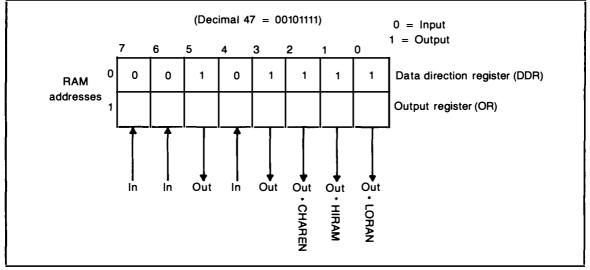

The microprocessor is located at 3 1/2 across and 1 1/2 down. The 6510 is a variation of the 6502, which has been one of the most used microprocessors in recent years. The important difference between the 6510 and its predecessor the 6502 is an extra I/O register in the 6510 that the 6502 does not have. The details of the additional register is discussed in Chapters 12 and 13. The register provides a tricky way to handle all the memory in the 64.

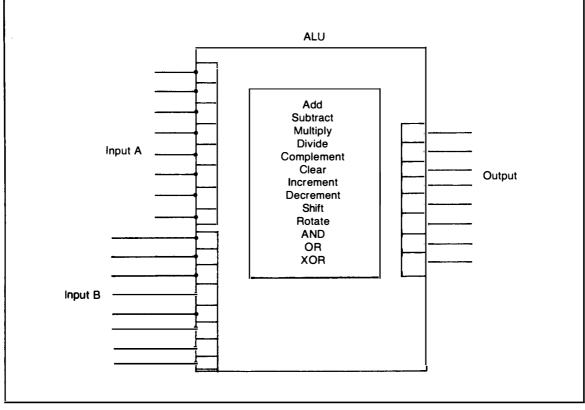

The MPU has the job of addressing all the residents of the memory map all around the board. It sends and receives data from the memory. It processes the data with the aid of its internal registers, its arithmetic and logic center, and its control section. The registers are temporary memory locations to store results in progress, incoming instructions, and memory map addresses that will have to be contacted during the data processing.

The arithmetic and logic center does the data processing. It is known as the ALU (Arithmetic

Logic Unit), and it performs all the calculations. It also selects, sorts, and compares the information according to the instructions it receives. The control section is a traffic cop in the MPU that keeps data traffic moving in the correct direction at the proper time.

## **Complex Interface Adapters**

The two 40-pin 6526 Complex Interface Adapters, or CIAs, are located at 1  $1/2 \times 1 1/2$ . The one closest to the left side of the board (CIA1) is used by the keyboard to enter data. The plug that the keyboard cable plugs into is next to the CIA, and you can see the copper etch tracks from the plug to the CIA pins.

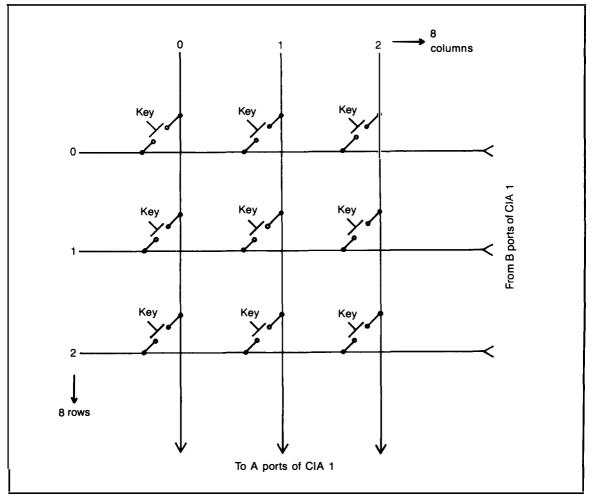

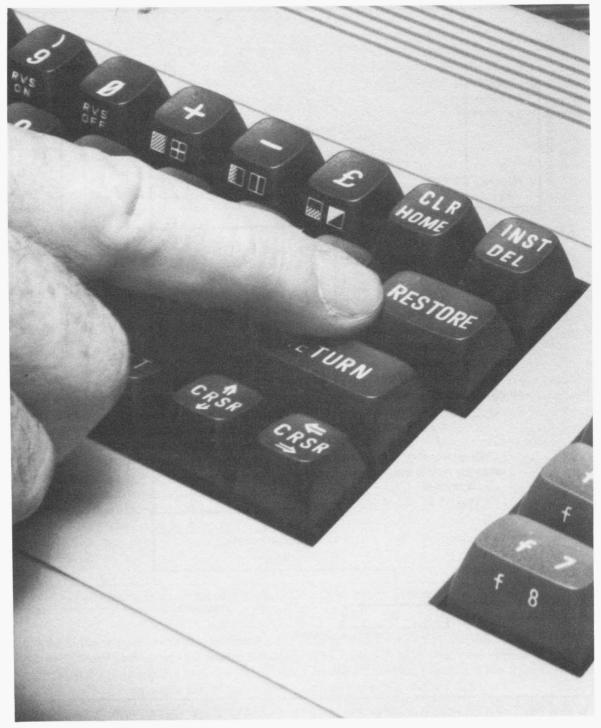

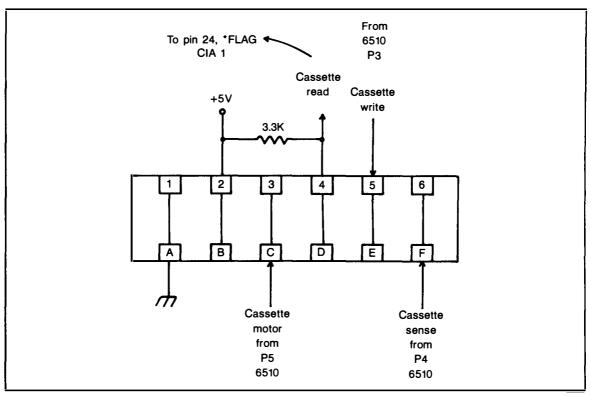

The keyboard is an arrangement of rows and columns that intersect. Everytime you hit a key a row is shorted to a column as Fig. 3-2 illustrates. There are eight rows and eight columns. This provides 64 ways that the rows and columns can short. Each short is transformed into a code for the character or symbol on the key. There is more detail about this setup in Chapter 16. The CIAs also provide entry or exit of signals to or from peripherals like the joysticks, user port, cassette, disk, printer, and other items that are interfaced to the 64.

These CIAs also have other important abilities that are discussed in Chapter 16. They deal with shift registers and internal timing circuits, including a time-of-day clock. In addition, the CIAs are able to produce interrupts which enable the MPU to service different circuits.

## Video Interface Chip

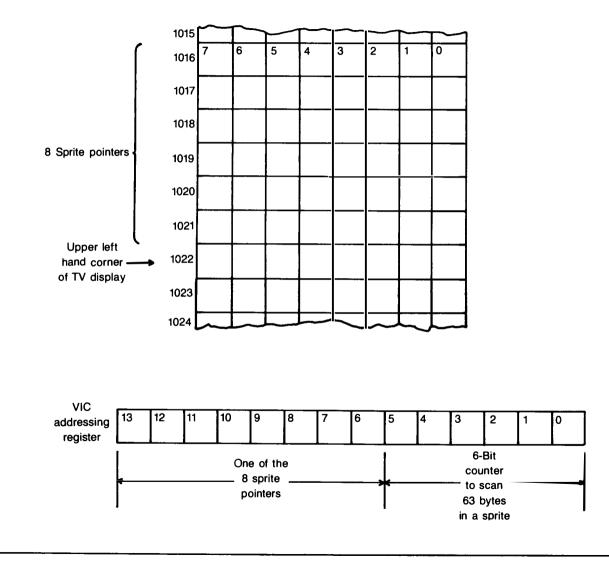

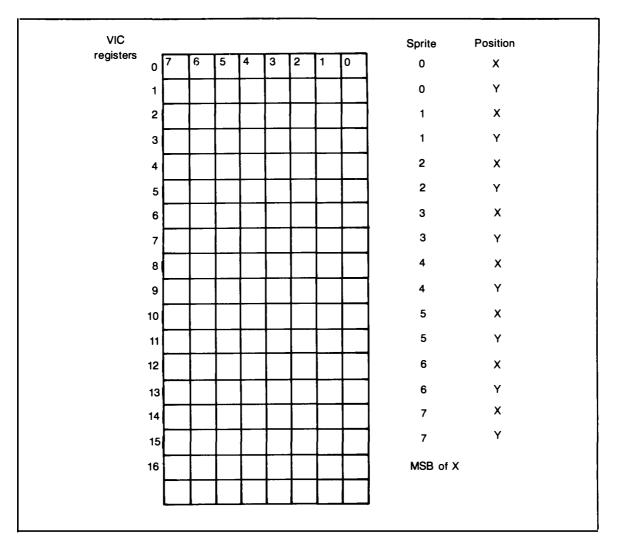

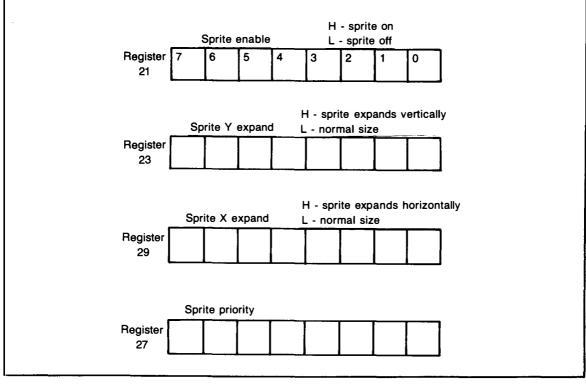

Under the metal shield at coordinates  $6 \times 3$  is the 40-pin 6567 Video Interface Chip. The VIC chip is the interface between the digital circuits and the analog video output circuits. The VIC produces many types of outputs that include variations of alphanumerics, semigraphics and pure graphics. One of the features of the VIC is its contribution in the creation of "sprites." A sprite is a high resolution programmable figure that can be put into a graphic display. It is used in sophisticated graphic

Fig. 3-2. The keyboard matrix is an arrangement of rows and columns. A row is shorted to a column when a key is pressed.

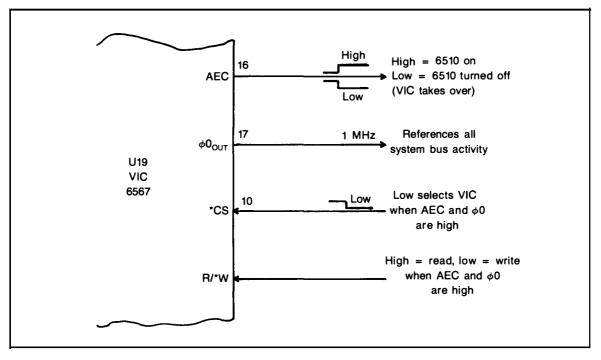

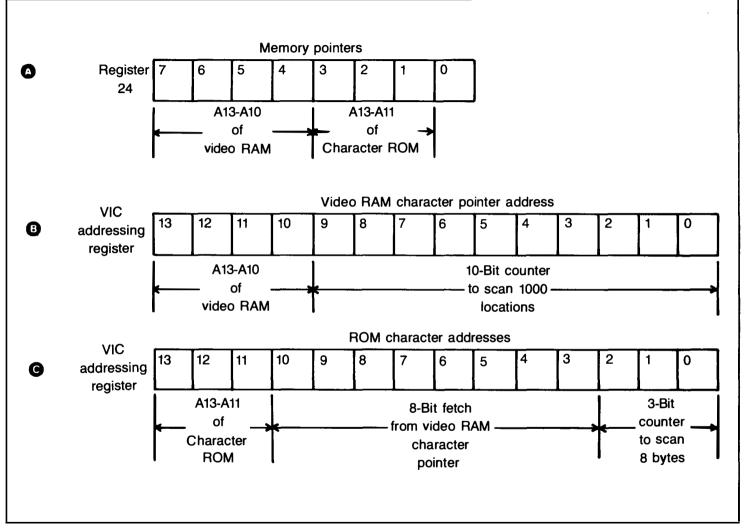

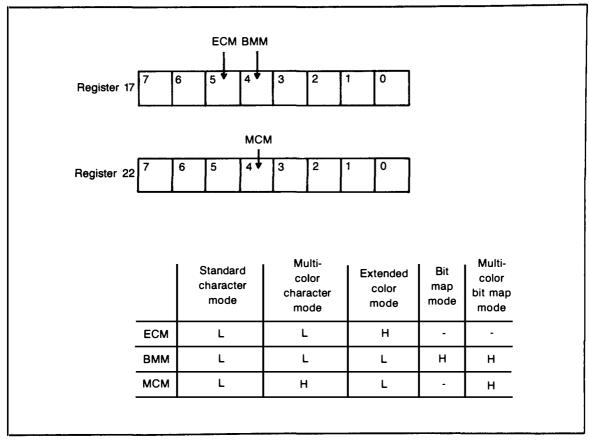

programs. A sprite can be formed in all types of conceivable shapes and be made to cavort freely around the TV display.