#### First Edition (April 1990)

The following paragraph does not apply to any state or country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. References to IBM products, programs, or services do not imply that IBM intends to make them available outside the United States.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be made in later editions. IBM may make improvements and/or changes in the product(s) and/or the program(s) at any time.

Address comments about this publication to IBM Corporation, Dept. F95/035-3, 740 New Circle Road N.W., Lexington, KY 40511 USA. Information you supply may be used by IBM without obligation.

For copies of publications related to this product, call toll free 1-800-IBM-7282 in the Continental USA. In Alaska, call 1-414-633-8108. In Canada, call toll free 1-800-465-1234. Other locations, contact your point of purchase.

IBM is a registered trademark of the International Business Machines Corporation.

Personal System/1 and PS/1 are trademarks of the International Business Machines Corporation.

#### © Copyright International Business Machines Corporation 1984, 1990. All rights reserved.

Note to US Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

## Preface

This technical reference provides system-specific hardware and software interface information for the IBM Personal System/1<sup>™</sup> computer. It is intended for developers who provide hardware and software products to operate with this system.

You should understand the concepts of computer architecture and programming before using this publication.

This manual is divided into the following sections.

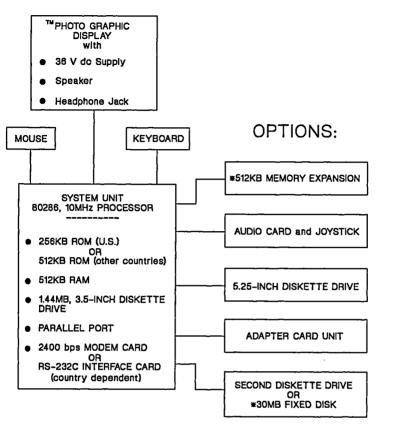

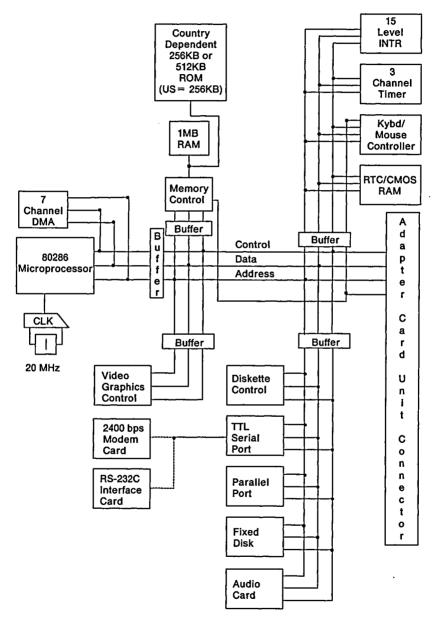

Section 1, "System Description" contains a description of IBM PS/1<sup>™</sup> computer and discusses system board features, an I/O address map, and system unit specifications.

Section 2, "System Board" discusses the operation of the system microprocessor, interrupts, system timers, and speaker.

Section 3, "System Board I/O Controllers" describes the input and output interfaces of the system board. This includes the operation of the keyboard/mouse controller, video subsystem, diskette drive controller, serial port controller, parallel port controller, and the different types of memory.

Section 4, "Power Supply" contains electrical input/output specifications and theory of operation for the power supply.

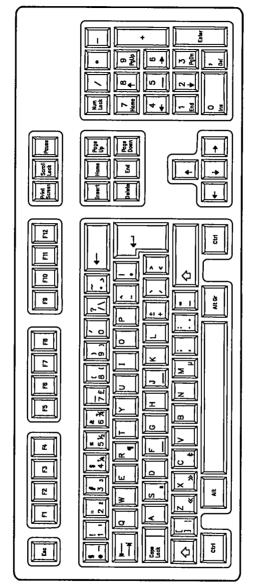

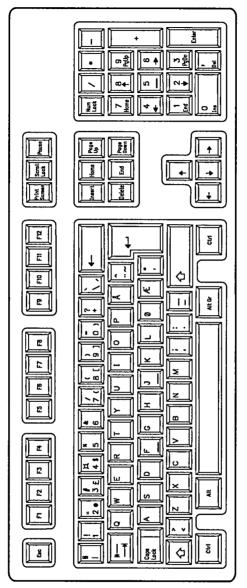

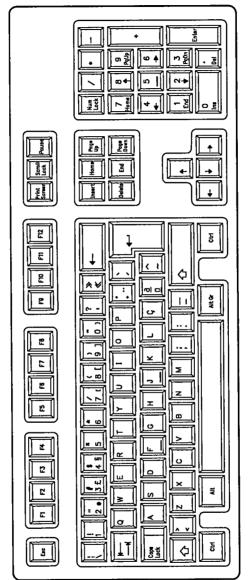

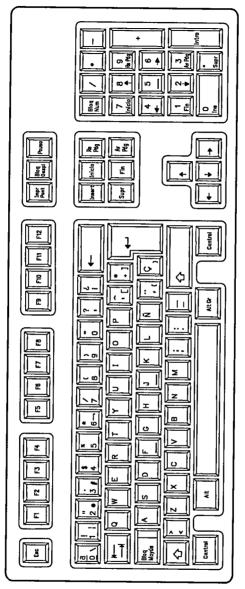

Section 5, "Keyboard" contains a description and specifications for the keyboard.

Section 6, "Mouse" contains a description and specifications for the mouse.

Section 7, "Displays" describes the Color or Black and White ™PHOTO GRAPHIC Displays.

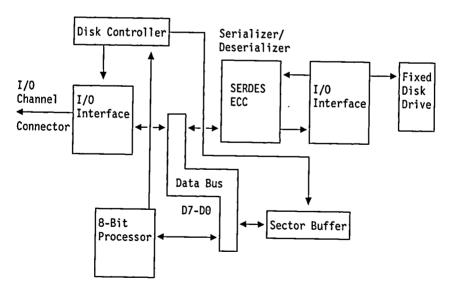

Section 8, "Drives" contains a description of the 3.5-inch 30MB fixed disk drive and controller and the 3.5-inch 1.44MB diskette drive.

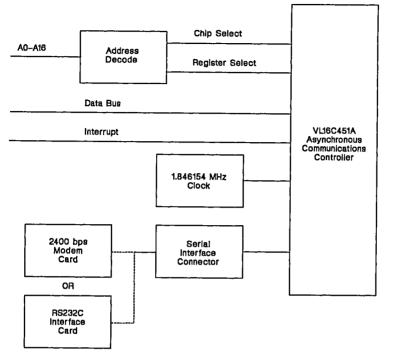

Section 9, "Modem/RS-232C Interface Cards" describes the 2400 bps modem card and the RS-232C interface card.

Section 10, "80286 Microprocessor Instruction Set" contains a quick reference for the 80286 assembly instruction set.

Section 11, "Characters and Keystrokes" contains the decimal and hexadecimal values for ASCII characters.

Section 12, "Compatibility" discusses guidelines to help developers design programs, adapters, and attachments that are compatible with other IBM Personal System/2 products and IBM Personal Computer products.

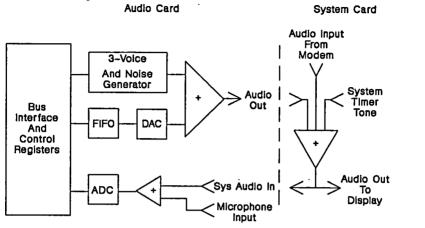

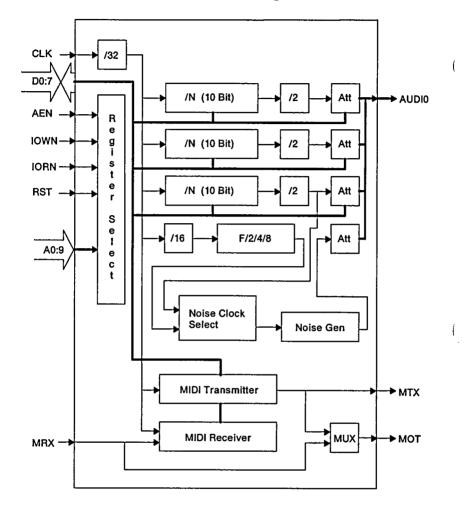

Appendix, "Options" contains features purchased separately, such as the 512KB memory expansion, audio card and joystick, 5.25-inch diskette drive unit, and adapter card unit.

A Glossary, Bibliography, and Index are also provided.

#### Suggested Related Publications:

- BIOS Interface Technical Reference for IBM PS/1™ Computer

- Hardware Maintenance Service for *IBM PS/1™ Computer*

- Using DOS 4.00

- DOS 4.00 Command Reference

- DOS 4.00 Technical Reference and Application Programming

(

IBM Personal Computer BASIC Reference.

## Contents

ĺ

(

1

| Section 1. System Description                                                                                                                | 1-1<br>1-3                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                              | 1_/                                          |

| System Board Features                                                                                                                        | 1-5                                          |

| System Board Locations                                                                                                                       | 1-5                                          |

| System Board Block Diagram                                                                                                                   | 1-0                                          |

| System I/O Address Map                                                                                                                       | 1-7                                          |

| Specifications                                                                                                                               | 1-8                                          |

| Section 2. System Board                                                                                                                      | 2-1                                          |

| Description                                                                                                                                  | 2-3                                          |

| System Microprocessor                                                                                                                        | 2-3                                          |

| Real Address Mode                                                                                                                            | 2-3                                          |

| Protected Virtual Address Mode                                                                                                               | 2-4                                          |

| Performance                                                                                                                                  | 2-4                                          |

|                                                                                                                                              | 2.5                                          |

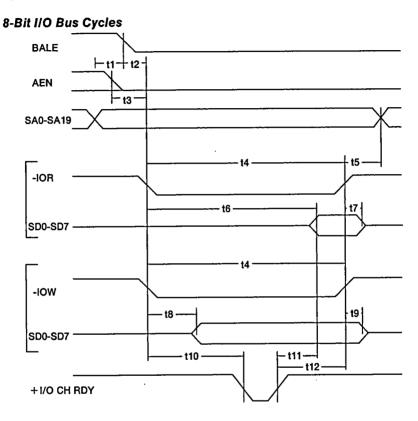

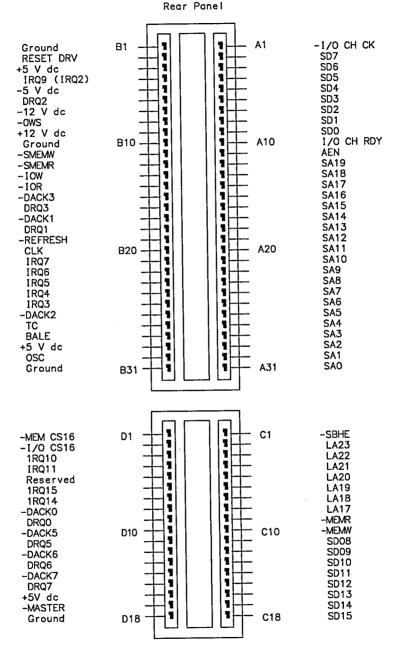

| Adapter Card Channel                                                                                                                         | 2-5                                          |

| Connector                                                                                                                                    | 2-0                                          |

| Signal Description                                                                                                                           | 2-11                                         |

| Olghar fallingo                                                                                                                              |                                              |

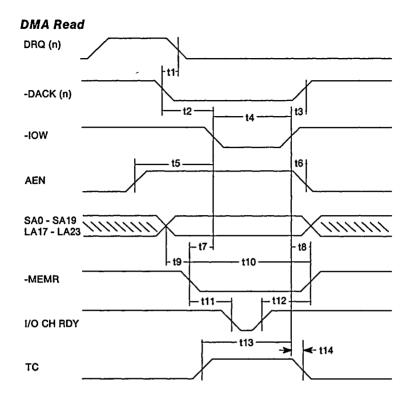

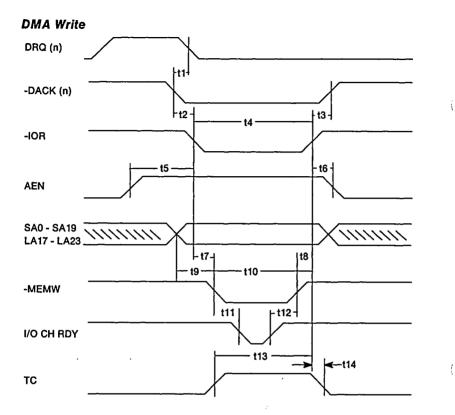

| DMA Controller                                                                                                                               | 2-19                                         |

| Data Transfers Between Memory and I/O Devices                                                                                                | 2-20                                         |

| Byte Pointer                                                                                                                                 | 2-20                                         |

| DMA Channels                                                                                                                                 | 2-20                                         |

| Page Register Addresses                                                                                                                      | 2-21                                         |

| DMA I/O Address Map                                                                                                                          | 2-23                                         |

| DMA Registers                                                                                                                                | 2-24                                         |

| Interrupts                                                                                                                                   | 2-28                                         |

| Non-Maskable Interrupt                                                                                                                       | 2-28                                         |

| Interrupt Assignments                                                                                                                        | 2-29                                         |

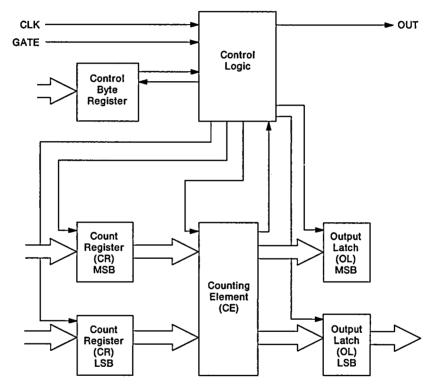

| System Timers                                                                                                                                | 2-31                                         |

| Channel 0 - System Timer                                                                                                                     | 2-32                                         |

| Channel 1 - Refresh Request Generator                                                                                                        | 2-32                                         |

| Channel 2 - Tone Generation for Speaker                                                                                                      | 2-32                                         |

| Timers 0, 1, and 2                                                                                                                           | 2-32                                         |

| Programming the System Timers                                                                                                                |                                              |

| Counter Write Operations                                                                                                                     | 2-32                                         |

|                                                                                                                                              | 2-32                                         |

|                                                                                                                                              | 2-33                                         |

| Counter Read Operations                                                                                                                      | 2-33<br>2-33                                 |

| Counter Read Operations                                                                                                                      | 2-33<br>2-33<br>2-34                         |

| Counter Read Operations                                                                                                                      | 2-33<br>2-33<br>2-34<br>2-35                 |

| Counter Read Operations       Registers         Registers       Counter Latch Command         System Timer Modes       Counter Latch Command | 2-33<br>2-33<br>2-34<br>2-35<br>2-36         |

| Counter Read Operations                                                                                                                      | 2-33<br>2-33<br>2-34<br>2-35<br>2-36<br>2-41 |

۰.

| Section 3. System Board I/O Controllers              | 3-1    |

|------------------------------------------------------|--------|

| Keyboard/Mouse Controller                            | 3-3    |

| Keyboard Password Security                           | 3-3    |

| Keyboard Controller Command and Status Bytes         | . 3-5  |

| Keyboard/Mouse Programming Considerations            | 3-9    |

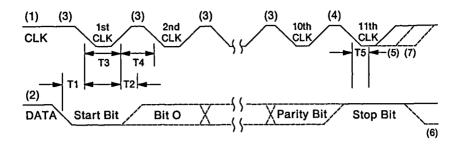

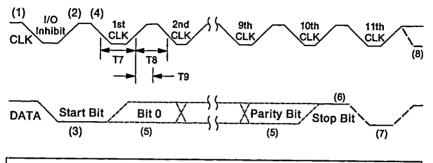

| Mouse/System Timings                                 | 3-10   |

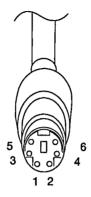

| Signals                                              | . 3-12 |

| Connector                                            | . 3-13 |

| Video Subsystem                                      | . 3-14 |

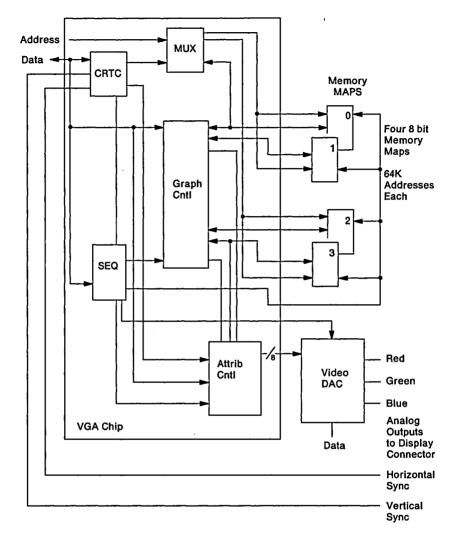

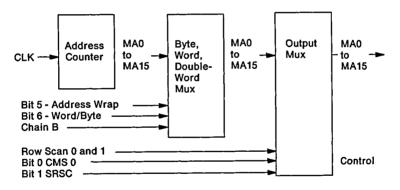

| VGA Components                                       | . 3-17 |

| BIOS ROM                                             | . 3-18 |

| Support Logic                                        | . 3-18 |

| Video Graphics Array Major Components                | . 3-18 |

| Modes of Operation                                   | . 3-22 |

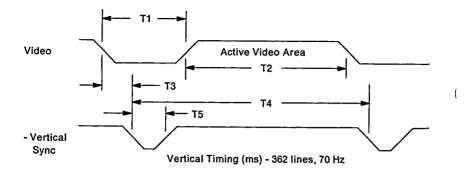

| Display Support                                      | . 3-23 |

| Video Subsystem Programmable Option Select           | . 3-24 |

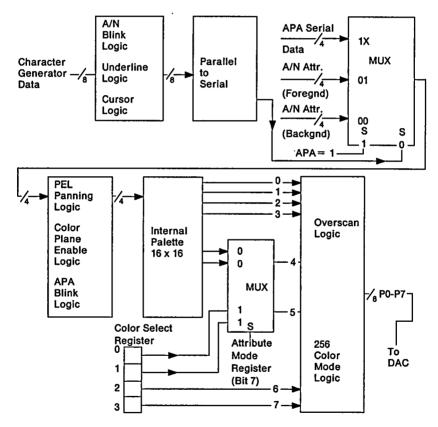

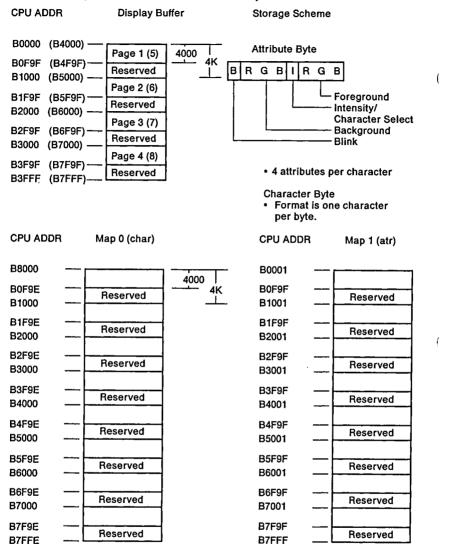

| Alphanumeric Modes                                   | . 3-25 |

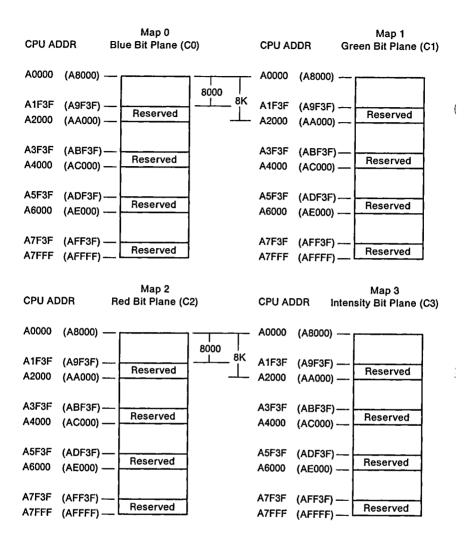

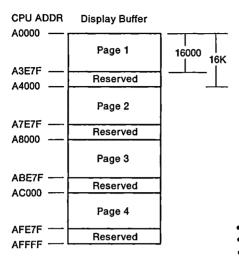

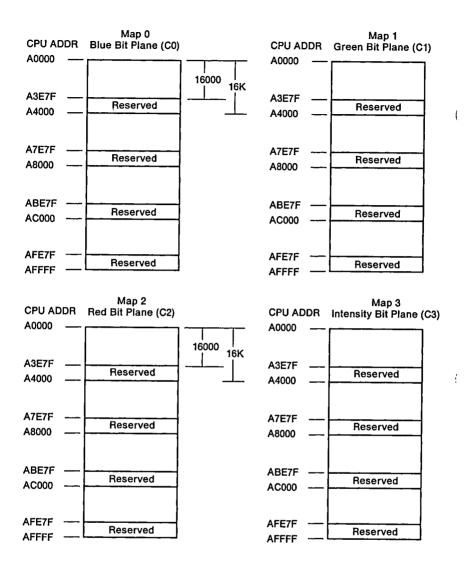

| Graphics Modes                                       | . 3-28 |

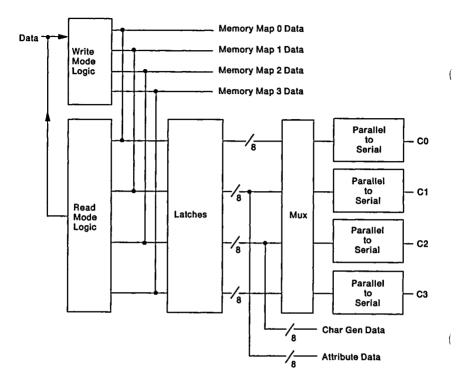

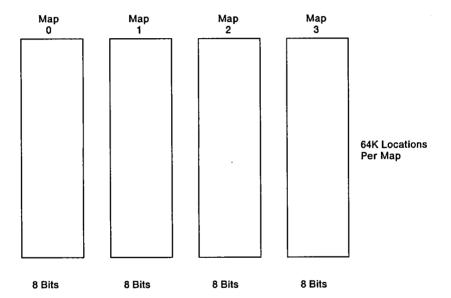

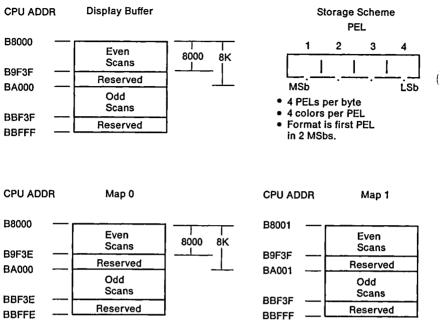

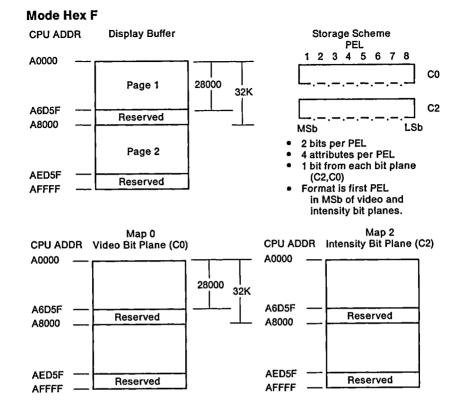

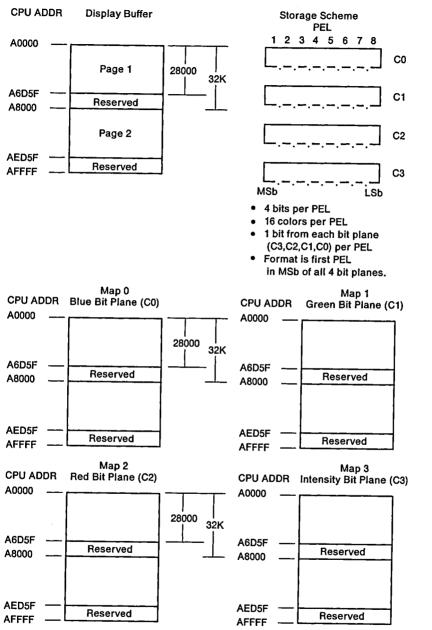

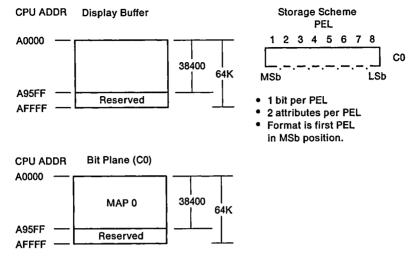

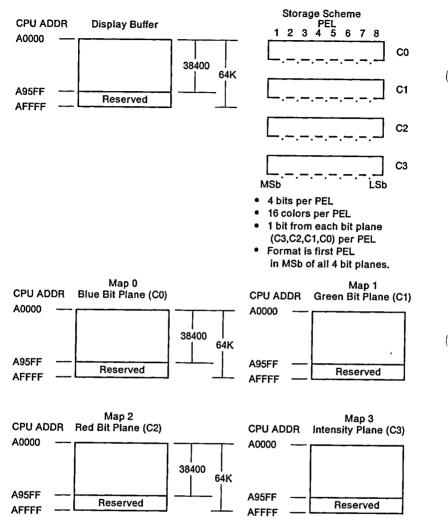

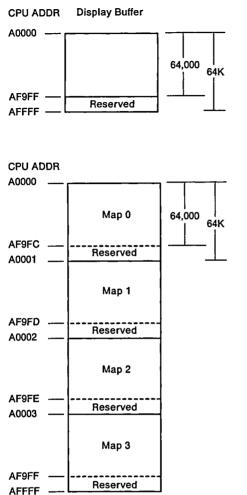

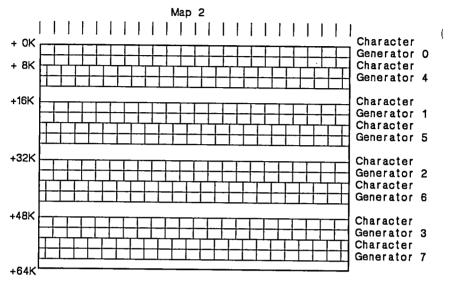

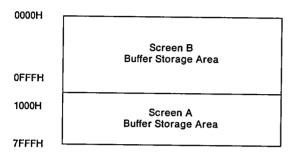

| Video Memory Organization                            | . 3-35 |

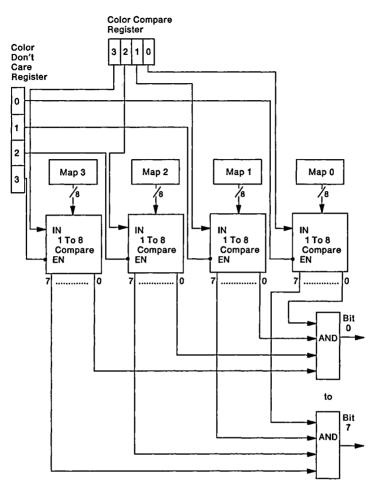

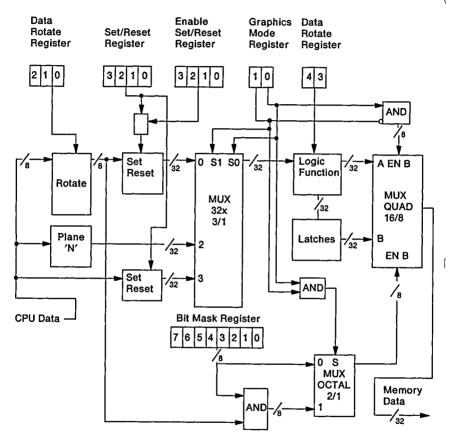

| Video Memory Read/Write Operations                   | . 3-50 |

| Registers                                            | . 3-53 |

| General Registers                                    | . 3-54 |

| Sequencer Registers                                  | . 3-58 |

| CRT Controller Registers                             | . 3-64 |

| Graphics Controller Registers                        | 3-79   |

| Attribute Controller Registers                       | 3-87   |

| VGA Programming Considerations                       | 3-93   |

| Video Digital-to-Analog Converter (Video DAC)        | 3-101  |

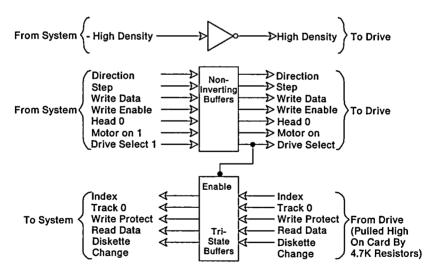

| Diskette Drive Controller                            | 3-111  |

| Registers                                            | 3-112  |

| Diskette Drive Controller Programming Considerations | 3-115  |

| Command Format                                       | 3-118  |

| Command Status Registers                             | 3-128  |

| Signal Descriptions                                  |        |

| Connector                                            | 3-134  |

| Serial Port Controller                               | 3-135  |

| Communications Application                           | 3-136  |

| Programmable Baud-Rate Generator                     | 3-137  |

| Registers                                            | 3-137  |

| Serial Port Controller Programming Considerations    | 3-147  |

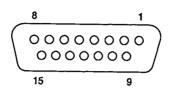

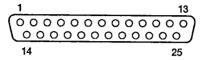

| Signal Descriptions                                  | 3-147  |

| System Board Voltage Interchange                     | 3-148  |

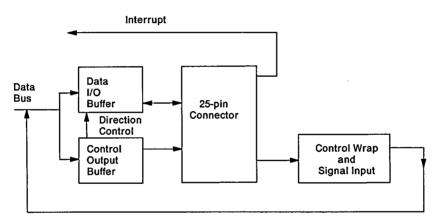

| Parallel Port Controller                             | 3-149  |

| Parallel Port Programmable Option Select             | 3-150  |

| Parallel Port Controller Programming Considerations  | 3-151  |

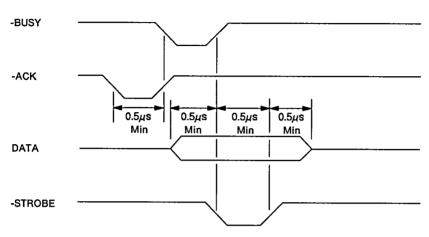

| Parallel Port Timing                                 | 3-154  |

ļ

(

1

ļ

| Signal Descriptions 3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 154        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

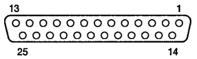

| Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 155        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 156        |

| Read-Only Memory (ROM) 3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 156        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·156       |

| Complementary Metal Oxide Semiconductor RAM 3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ·158       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -162       |

| Miscellaneous System Ports 3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -165       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -165       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -166       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -167       |

| System Condition of the (non Cool)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| Section 4. Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1        |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3        |

| Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-3        |

| Power Controller Coordination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-3        |

| Output Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-3        |

| Voltage Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-4        |

| No-Load Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-4        |

| Auto Restart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-4        |

| Power Good Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-4        |

| Power Card Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-5        |

| Power/Audio Cable Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-6        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>+ v</b> |

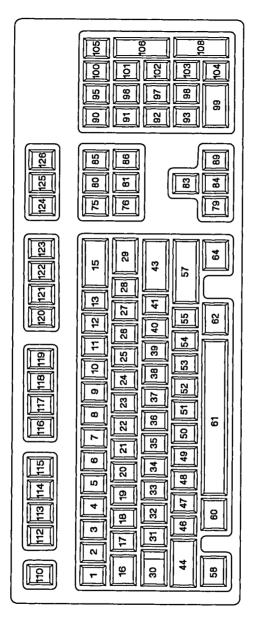

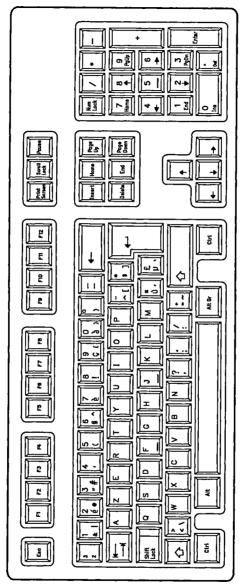

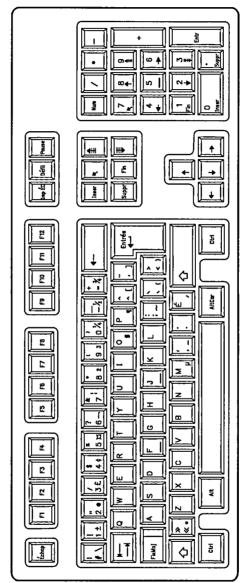

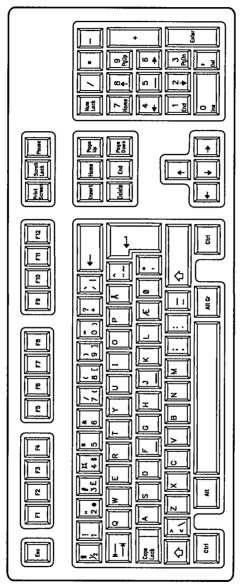

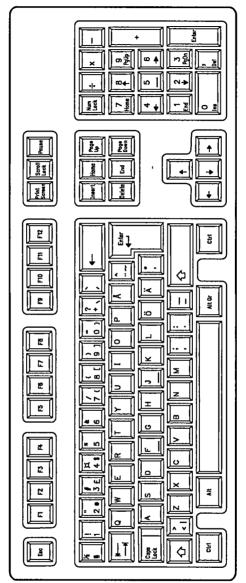

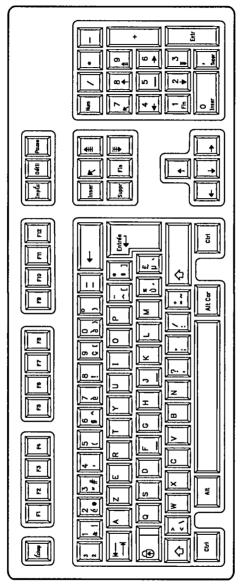

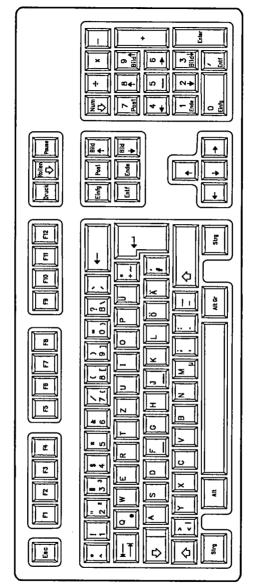

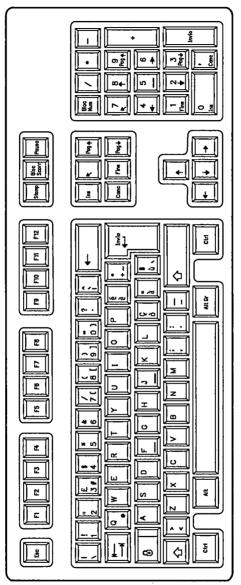

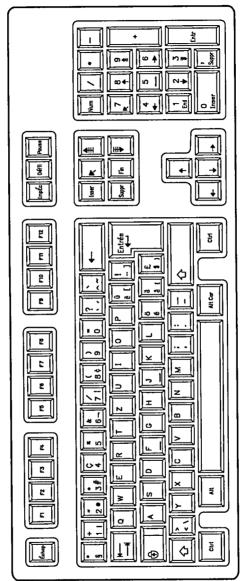

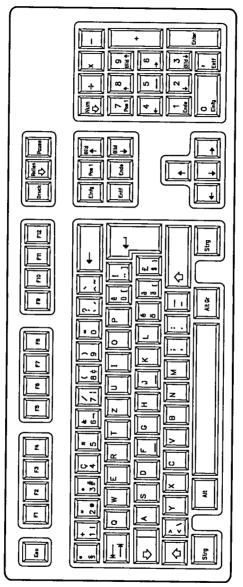

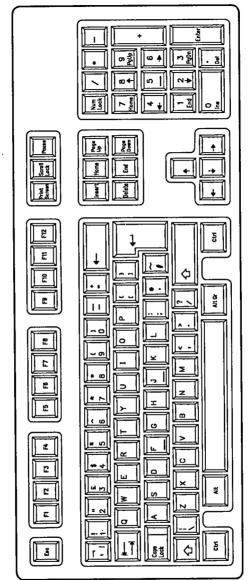

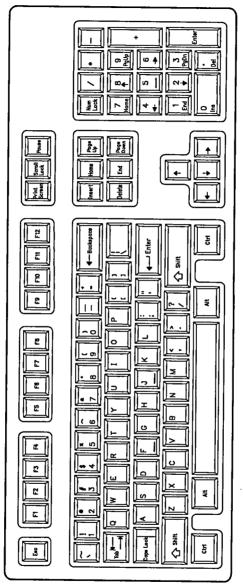

| Section 5. Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-1        |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-3        |

| Keyboard Charts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-3        |

| Belgium (Dutch) Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-6        |

| Canada (French) Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-7        |